Virtex-5 FPGA User Guide www.xilinx.com 233

UG190 (v5.0) June 19, 2009

Virtex-5 FPGA SelectIO Primitives

Virtex-5 FPGA SelectIO Primitives

The Xilinx software library includes an extensive list of primitives to support a variety of

I/O standards available in the Virtex-5 FPGA I/O primitives. The following are five

generic primitive names representing most of the available single-ended I/O standards.

• IBUF (input buffer)

• IBUFG (clock input buffer)

• OBUF (output buffer)

• OBUFT (3-state output buffer)

• IOBUF (input/output buffer)

These six generic primitive names represent most of the available differential I/O

standards:

• IBUFDS (input buffer)

• IBUFGDS (clock input buffer)

• OBUFDS (output buffer)

• OBUFTDS (3-state output buffer)

• IOBUFDS (input/output buffer)

• IBUFDS_DIFF_OUT (input buffer)

IBUF and IBUFG

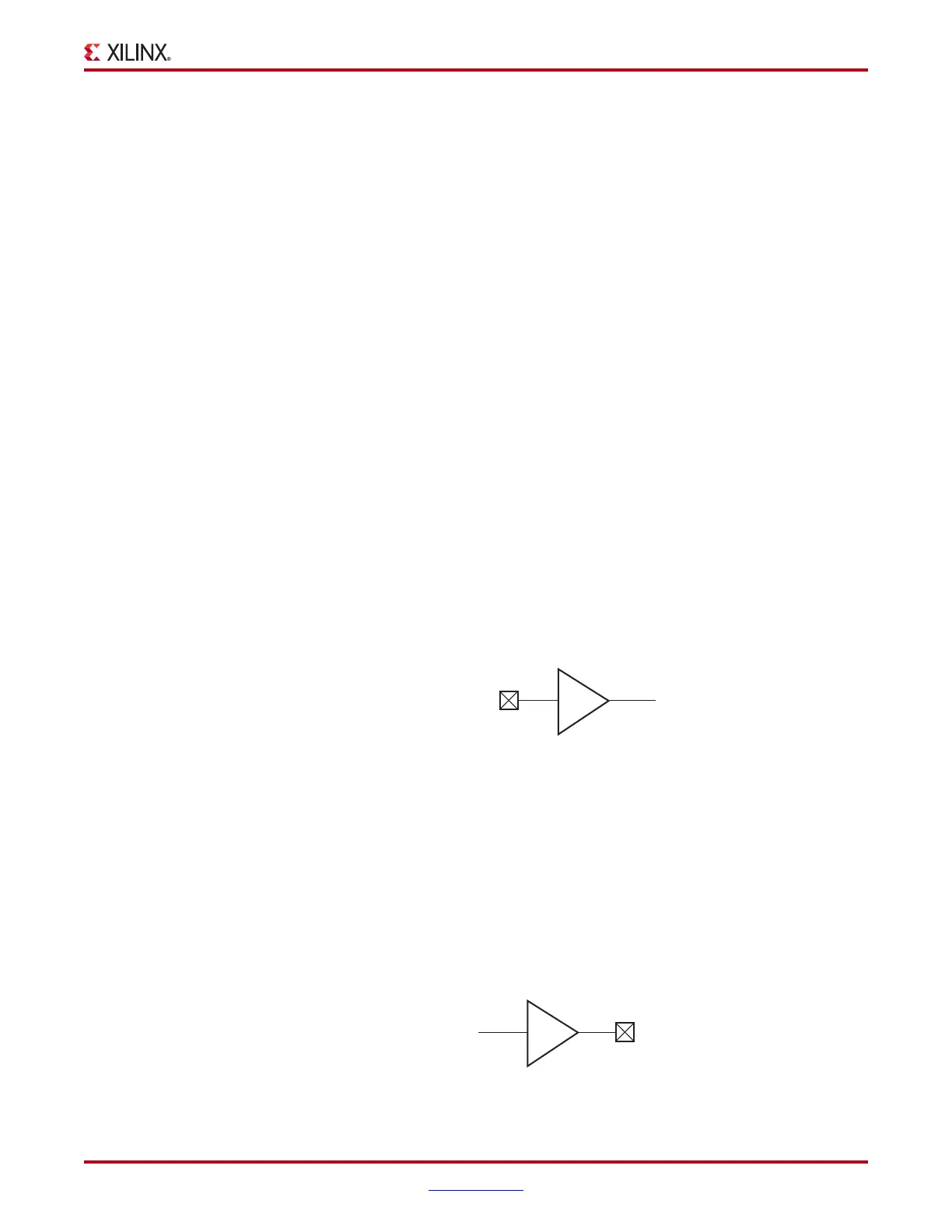

Signals used as inputs to Virtex-5 devices must use an input buffer (IBUF). The generic

Virtex-5 FPGA IBUF primitive is shown in Figure 6-18.

The IBUF and IBUFG primitives are the same. IBUFGs are used when an input buffer is

used as a clock input. In the Xilinx software tools, an IBUFG is automatically placed at

clock input sites.

OBUF

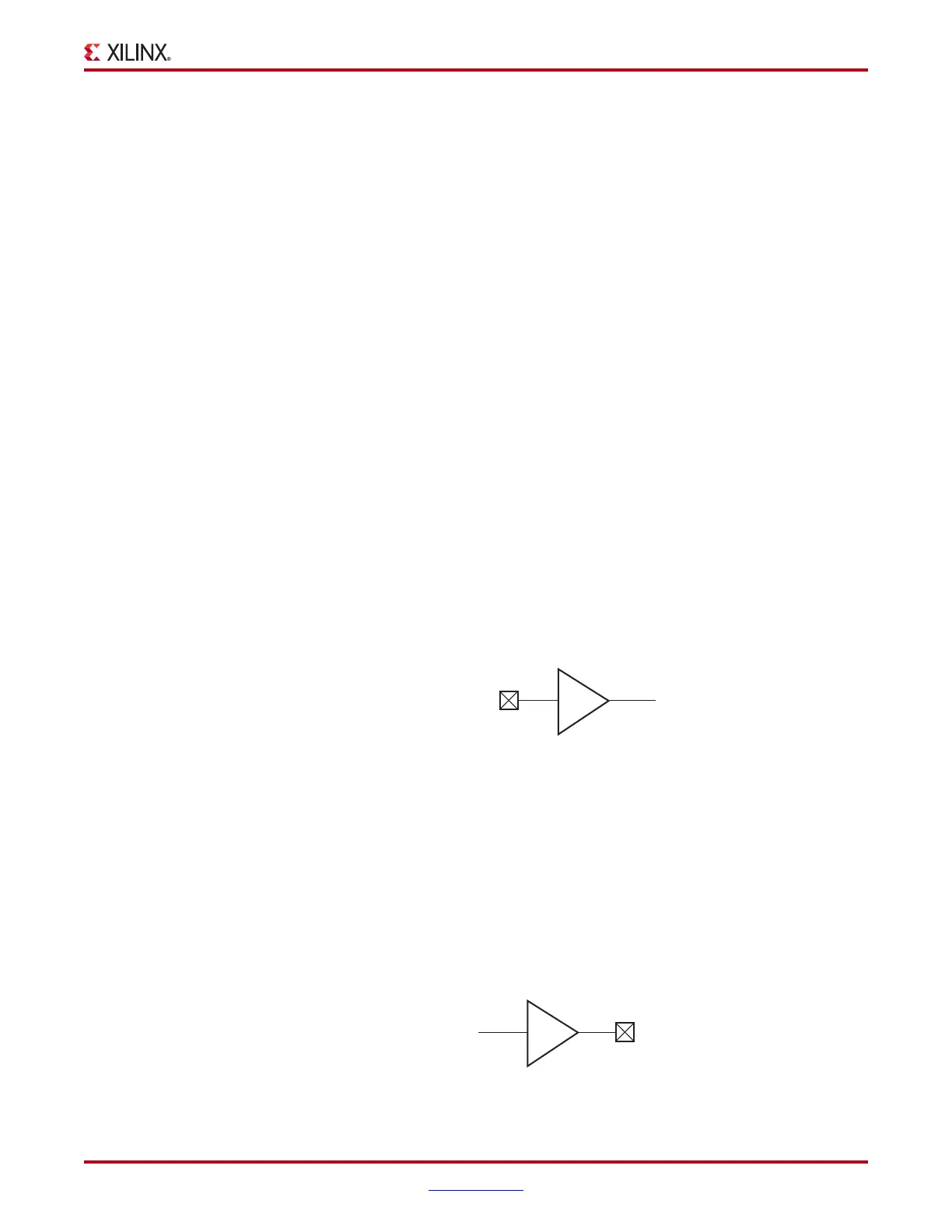

An output buffer (OBUF) must be used to drive signals from Virtex-5 devices to external

output pads. A generic Virtex-5 FPGA OBUF primitive is shown in Figure 6-19.

X-Ref Target - Figure 6-18

Figure 6-18: Input Buffer (IBUF/IBUFG) Primitives

ug190_6_16_022806

IBUF/IBUFG

O (Output)

into FPGA

I (Input)

From device pad

X-Ref Target - Figure 6-19

Figure 6-19: Output Buffer (OBUF) Primitive

ug190_6_17_022806

OBUF

O (Output)

to device pad

I (Input)

From FPGA

Loading...

Loading...