Virtex-5 FPGA User Guide www.xilinx.com 365

UG190 (v5.0) June 19, 2009

Input Serial-to-Parallel Logic Resources (ISERDES)

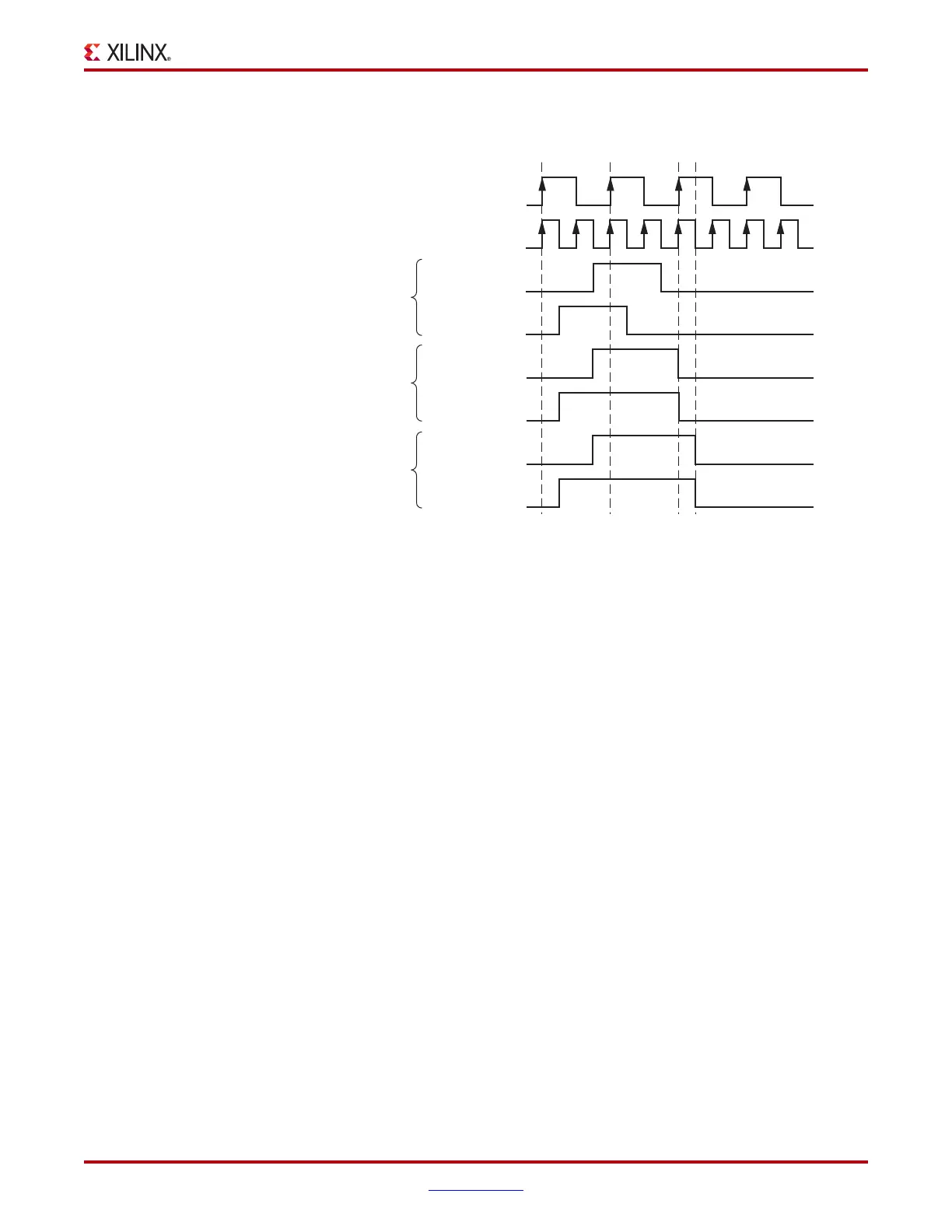

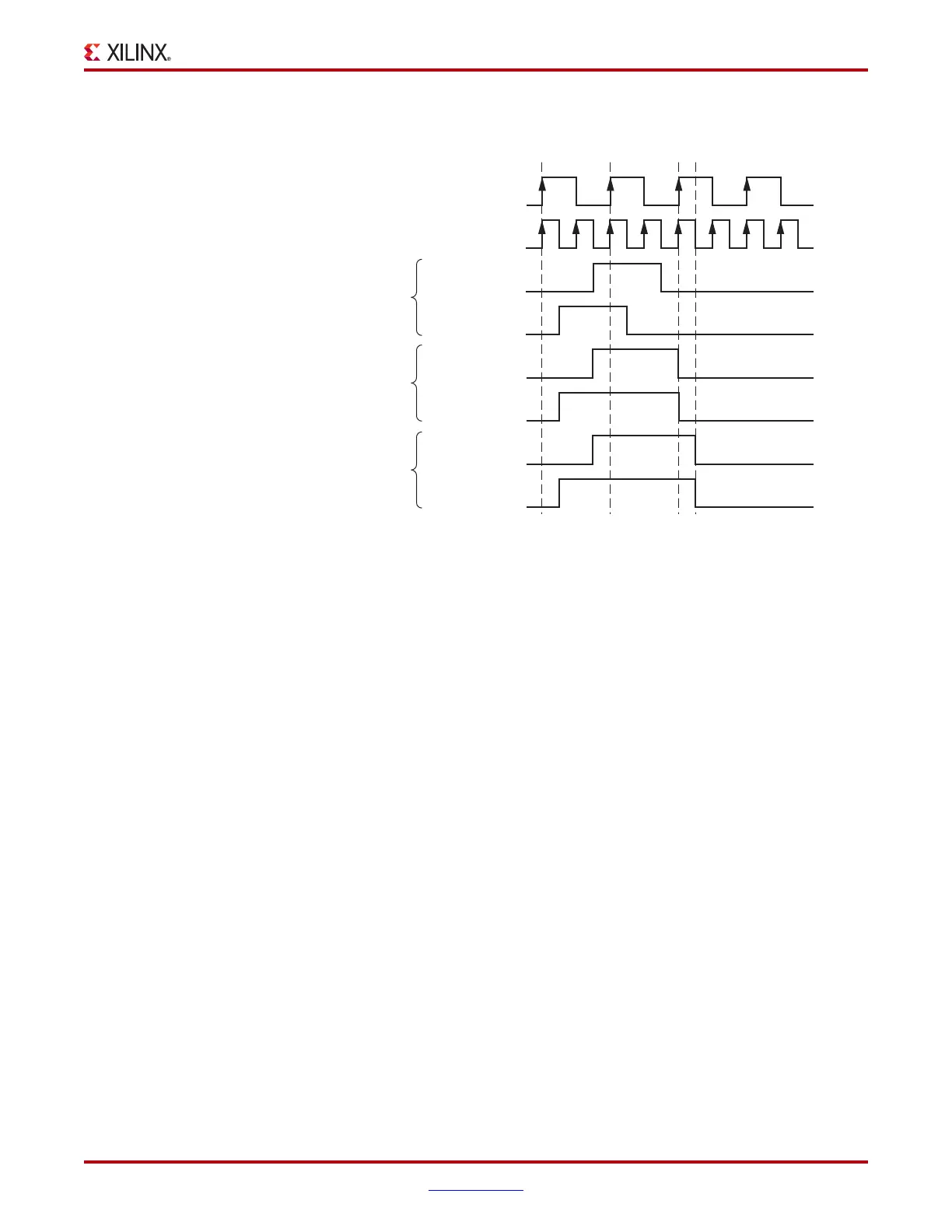

Clock Event 2

The reset pulse is deasserted on the rising edge of CLKDIV. The difference in propagation

delay between the two ISERDES causes the RST input to come out of reset on two different

CLK cycles. Without internal retiming, ISERDES1 finishes reset one CLK cycle before

ISERDES0 and both ISERDES are asynchronous.

Clock Event 3

The release of the reset signal at the RST input is retimed internally to CLKDIV. This

synchronizes ISERDES0 and ISERDES1.

Clock Event 4

The release of the reset signal at the RST input is retimed internally to CLK.

ISERDES VHDL and Verilog Instantiation Template

VHDL and Verilog instantiation templates are available in the Libraries Guide for all

primitives and submodules.

In VHDL, each template has a component declaration section and an architecture section.

Each part of the template should be inserted within the VHDL design file. The port map of

the architecture section should include the design signal names.

X-Ref Target - Figure 8-9

Figure 8-9: Two ISERDES Coming Out of Reset Synchronously with One Another

UG190_8_09_110707

CLKDIV

ISERDES0

Signal at

RST Input

ISERDES1

ISERDES0

ISERDES1

ISERDES0

ISERDES1

CLK

Clock

Event 1

Clock

Event 2

Clock

Event 3

Clock

Event 4

Internal Reset

(CLKDIV)

Internal Reset

(CLK)

Loading...

Loading...