Virtex-5 FPGA User Guide www.xilinx.com 57

UG190 (v5.0) June 19, 2009

DCM Ports

When LOCKED is Low (during reset or the locking process), all the status signals are

deasserted Low.

Dynamic Reconfiguration Ready Output - DRDY

The dynamic reconfiguration ready (DRDY) output pin provides the response to the DEN

signal for the DCM’s dynamic reconfiguration feature. Further information on the DRDY

pin is available in the dynamic reconfiguration section in the Virtex-5 FPGA Configuration

Guide.

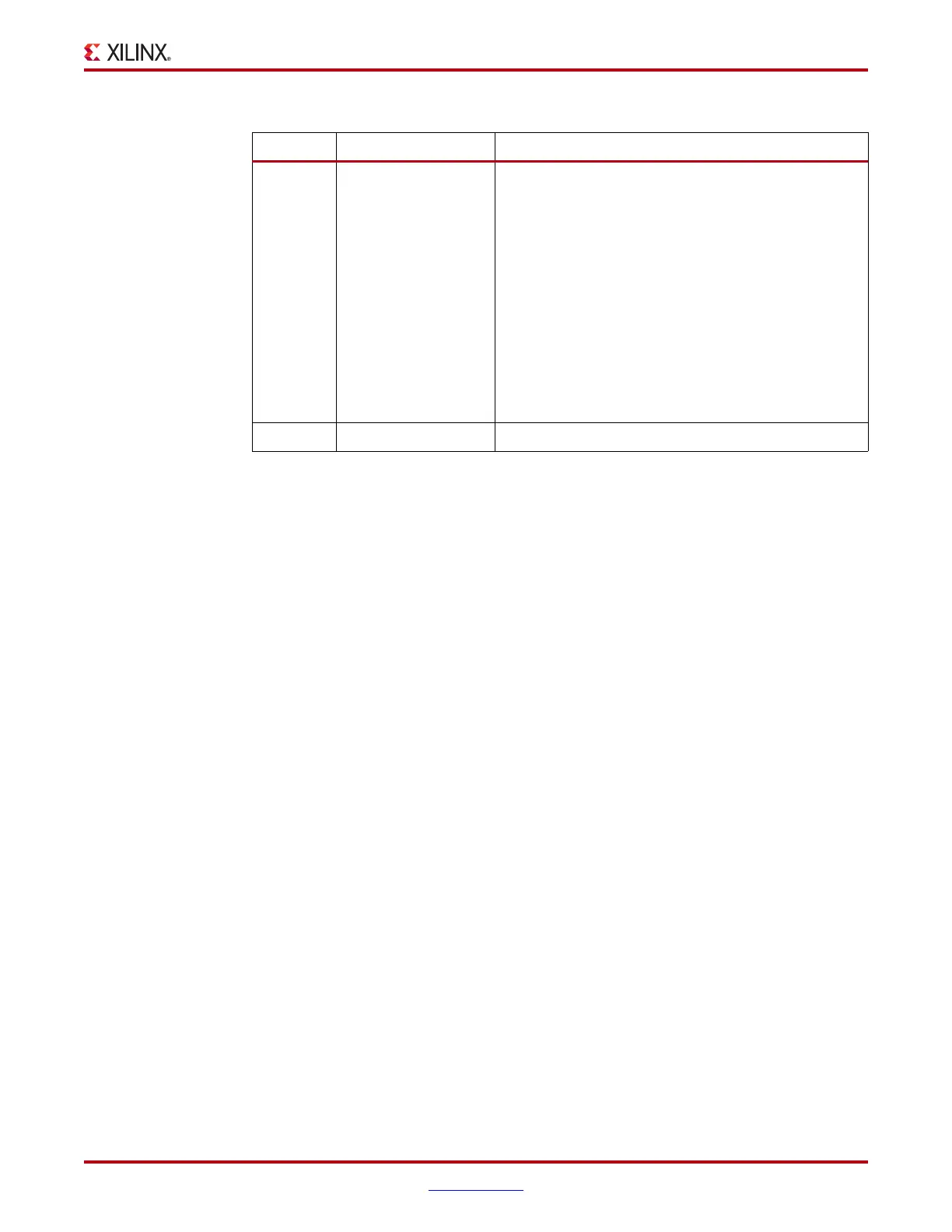

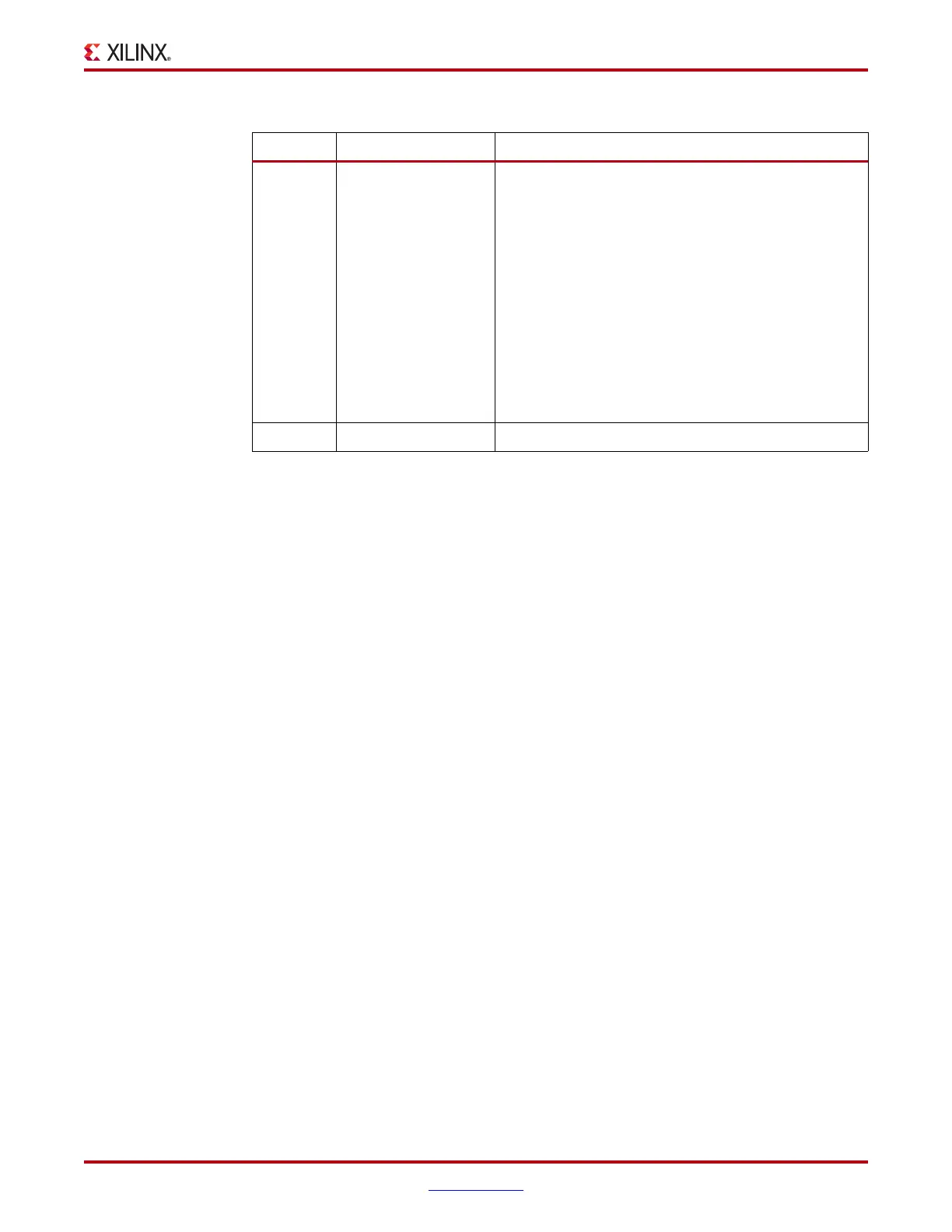

DO[3] CLKFB stopped Asserted when the feedback clock is stopped (CLKFB

remains High or Low for one or more clock cycles). The

DO[3] CLKFB stopped status is asserted within six

CLKIN cycles after CLKFB is stopped. CLKFB stopped

will deassert within six CLKIN cycles when CLKFB

resumes after being stopped momentarily. An

occasionally skipped CLKFB does not affect the DCM

operation. However, stopping CLKFB for a long time

can result in the DCM losing LOCKED. When LOCKED

is lost, the DCM needs to be reset to resume operation.

When the DLL portion of the DCM is not used (for

example, when using CLKFX output only), the CLKFB

can be left unconnected. In this case, DO[3] is

deasserted.

DO[15:4] Not assigned

Table 2-4: DCM Status Mapping to DO Bus (Continued)

DO Bit Status Description

Loading...

Loading...