234 www.xilinx.com Virtex-5 FPGA User Guide

UG190 (v5.0) June 19, 2009

Chapter 6: SelectIO Resources

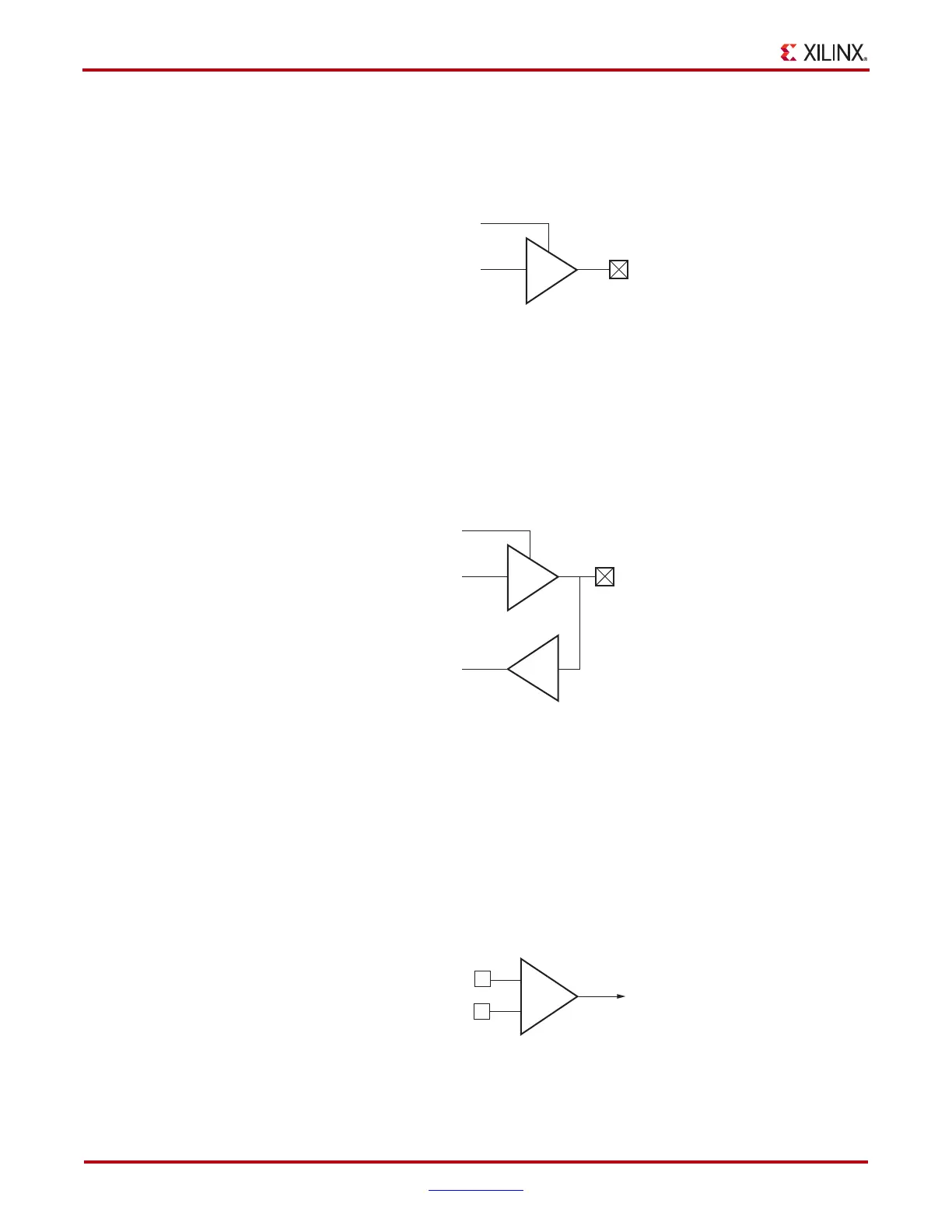

OBUFT

The generic 3-state output buffer OBUFT, shown in Figure 6-20, typically implements

3-state outputs or bidirectional I/O.

IOBUF

The IOBUF primitive is needed when bidirectional signals require both an input buffer and

a 3-state output buffer with an active High 3-state pin. Figure 6-21 shows a generic Virtex-5

FPGA IOBUF.

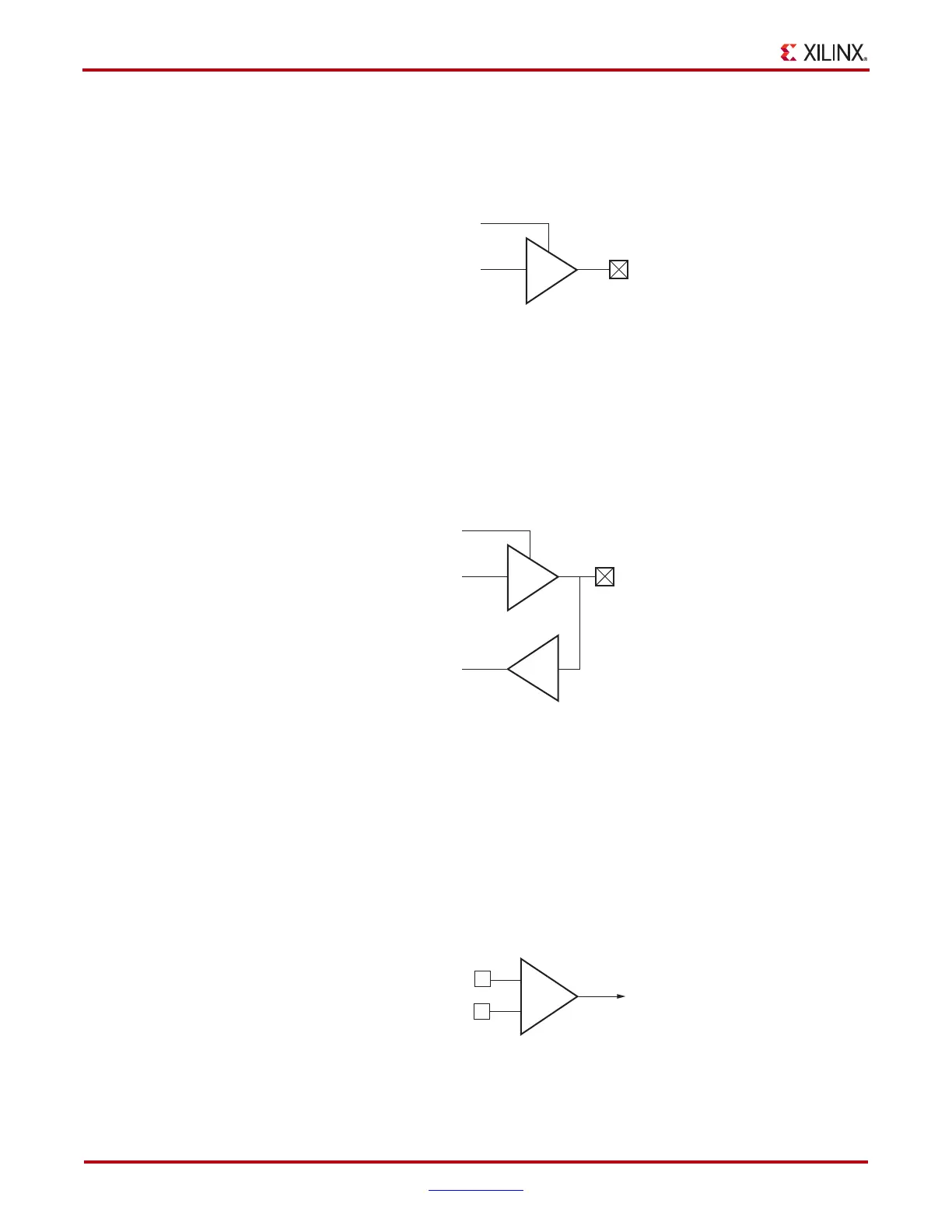

IBUFDS and IBUFGDS

The usage and rules corresponding to the differential primitives are similar to the single-

ended SelectIO primitives. Differential SelectIO primitives have two pins to and from the

device pads to show the P and N channel pins in a differential pair. N channel pins have a

“B” suffix.

Figure 6-22 shows the differential input buffer primitive

X-Ref Target - Figure 6-20

Figure 6-20: 3-State Output Buffer (OBUFT) Primitive

ug190_6_18_022806

OBUFT

O (Output)

to device pad

I (Input)

From FPGA

T

3-state input

X-Ref Target - Figure 6-21

Figure 6-21: Input/Output Buffer (IOBUF) Primitive

ug190_6_19_022806

IOBUF

I/O

to/from device pad

I (Input)

from FPGA

O (Output)

to FPGA

T

3-state input

X-Ref Target - Figure 6-22

Figure 6-22: Differential Input Buffer Primitive (IBUFDS/IBUFGDS)

ug190_6_20_022806

+

–

I

IB

O

IBUFDS/IBUFGDS

Inputs from

device pads

Output to

FPGA

Loading...

Loading...