354 www.xilinx.com Virtex-5 FPGA User Guide

UG190 (v5.0) June 19, 2009

Chapter 8: Advanced SelectIO Logic Resources

• Dedicated support for Networking interfaces.

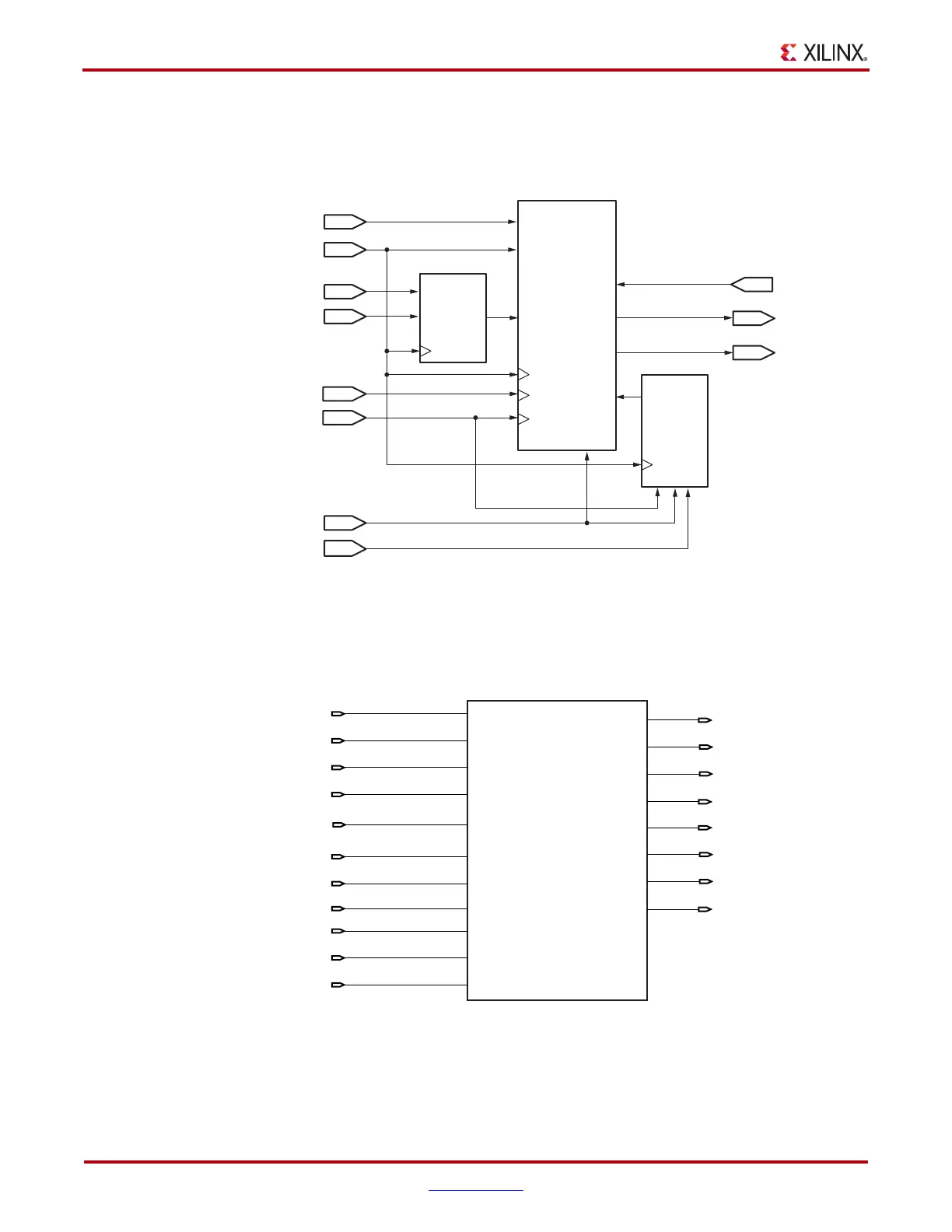

Figure 8-1 shows the block diagram of the ISERDES, highlighting all the major

components and features of the block.

ISERDES Primitive (ISERDES_NODELAY)

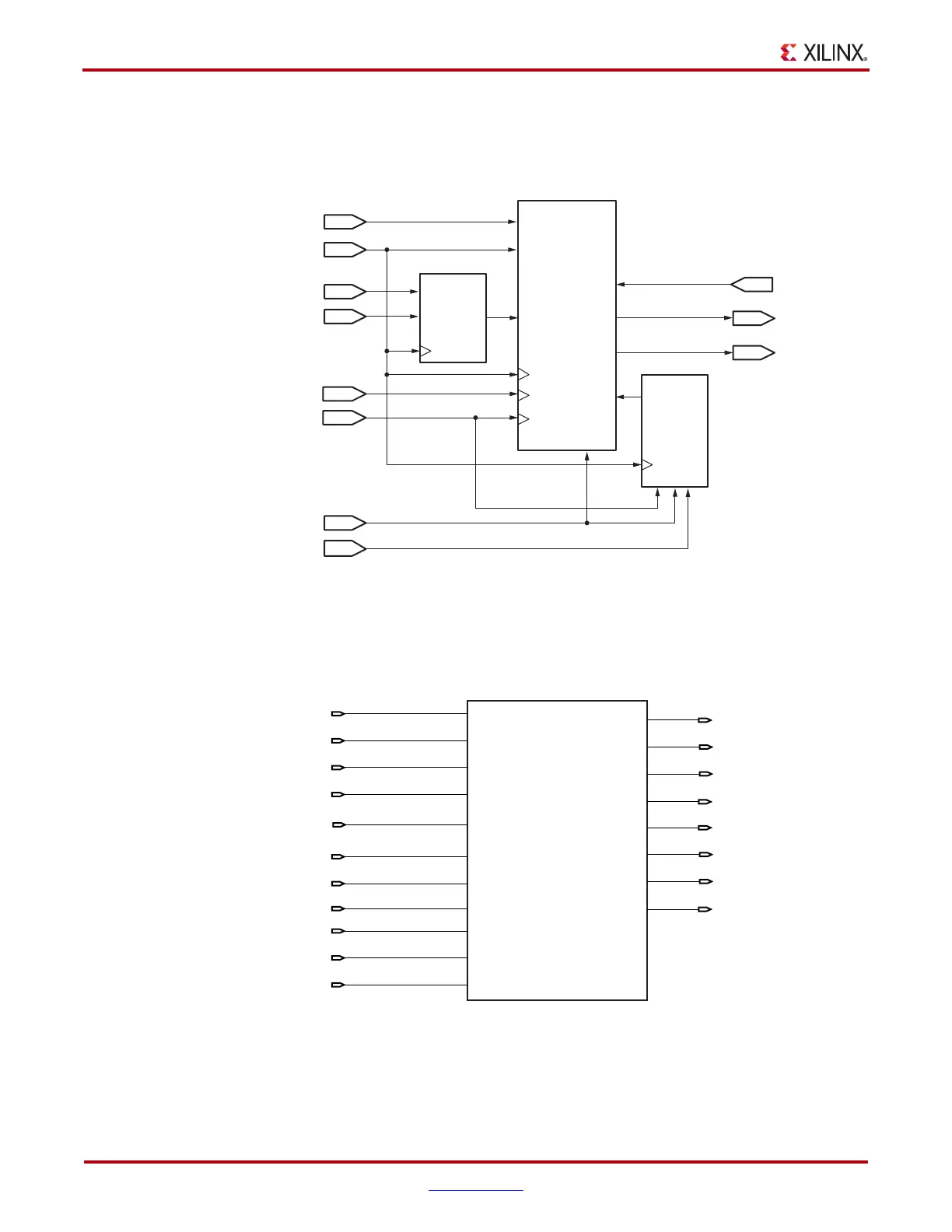

The ISERDES primitive in Virtex-5 devices (shown in Figure 8-2) is ISERDES_NODELAY.

X-Ref Target - Figure 8-1

Figure 8-1: ISERDES Block Diagram

D

CLKDIV

Serial to Parallel

Converter

BITSLIP

Module

CE

Module

OCLK

CLK

CE1

CE2

Q1 - Q6

SHIFTOUT1/2

SHIFTIN1/2

RST

Bitslip

ug190_8_01_050906

X-Ref Target - Figure 8-2

Figure 8-2: ISERDES_NODELAY Primitive

BITSLIP

CE1

CE2

CLK

CLKDIV

CLKB

D

OCLK

SHIFTIN1

SHIFTIN2

RST

SHIFTOUT1

SHIFTOUT2

Q5

Q6

Q3

Q4

Q1

Q2

ug190_8_02_112607

ISERDES_NODELAY

Primitive

Loading...

Loading...