250 www.xilinx.com Virtex-5 FPGA User Guide

UG190 (v5.0) June 19, 2009

Chapter 6: SelectIO Resources

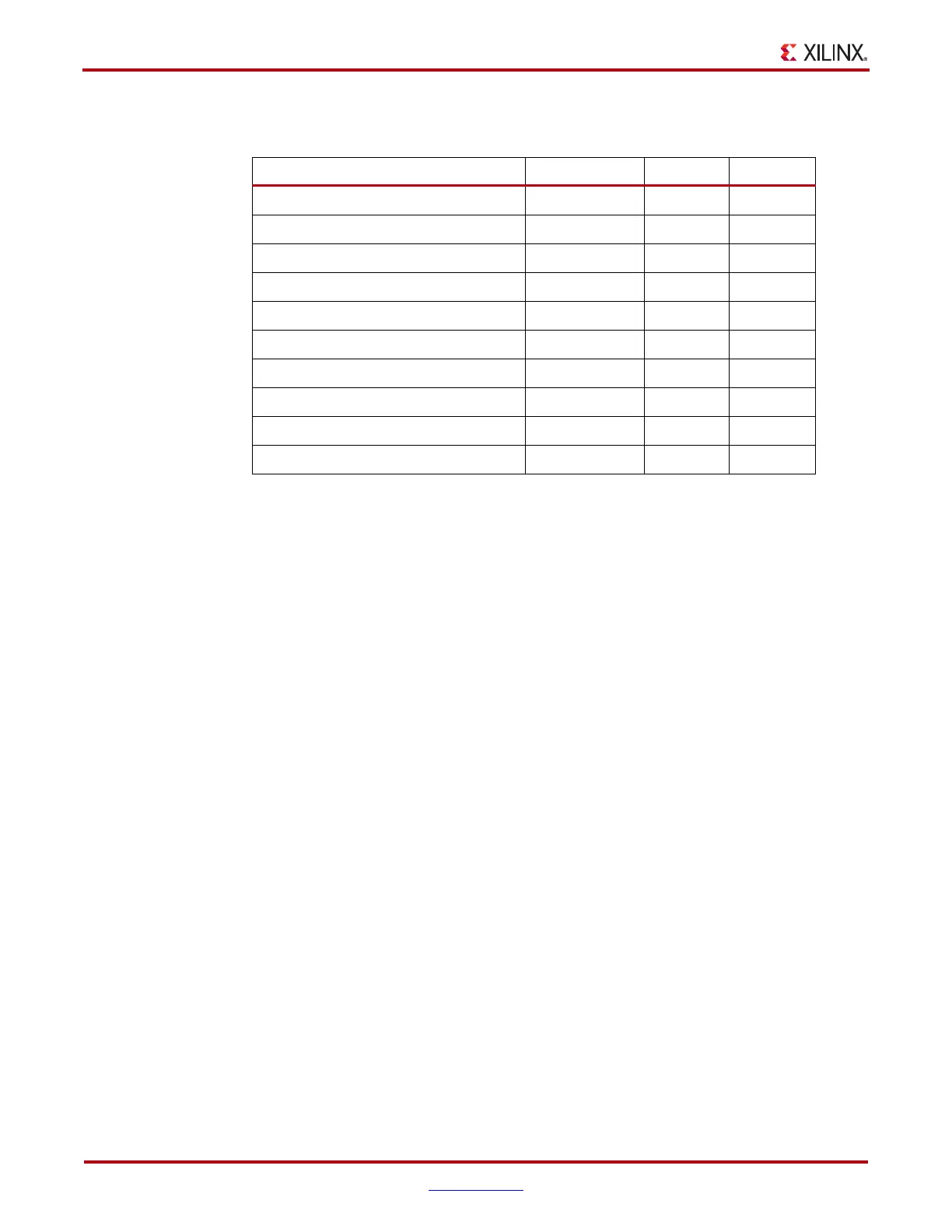

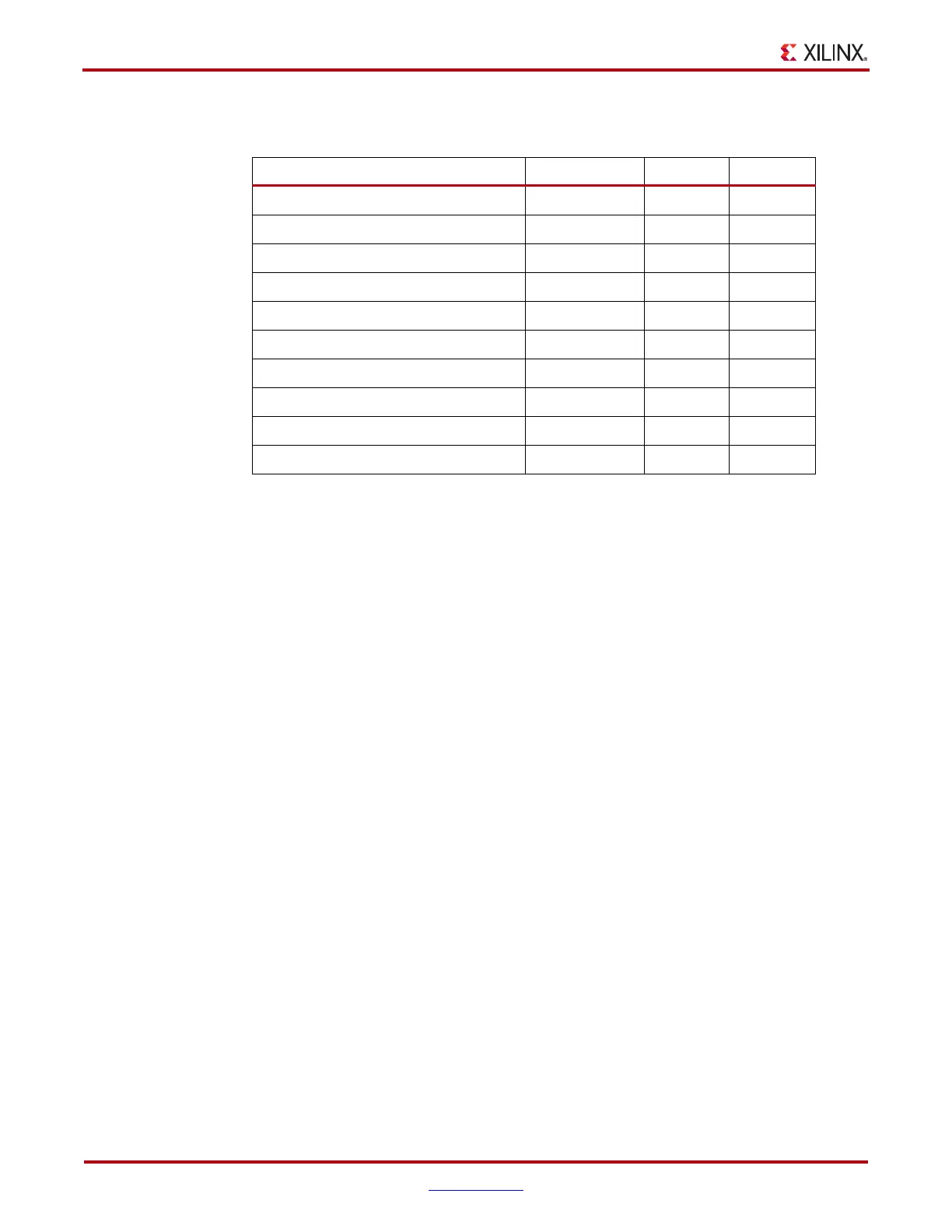

Table 6-14 lists the GTLP DC voltage specifications.

HSTL (High-Speed Transceiver Logic)

The High-Speed Transceiver Logic (HSTL) standard is a general-purpose high-speed bus

standard sponsored by IBM (EIA/JESD8-6). The 1.5V and 1.8V have four variations or

classes. To support clocking high-speed memory interfaces, a differential version of this

standard was added. Virtex-5 FPGA I/O supports all four classes for 1.5V and 1.8V and the

differential versions of classes I and II. These differential versions of the standard require a

differential amplifier input buffer and a push-pull output buffer.

HSTL_ I, HSTL_ III, HSTL_ I_18, HSTL_ III_18, HSTL_I_12

HSTL_I uses V

CCO

/2 as a parallel termination voltage (V

TT

). HSTL_III uses V

CCO

as a

parallel termination voltage (V

TT

). HSTL_I and HSTL_III are intended to be used in

unidirectional links.

HSTL_ I_DCI, HSTL_ III_DCI, HSTL_ I_DCI_18, HSTL_ III_DCI_18

HSTL_I_DCI provides on-chip split thevenin termination powered from V

CCO

, creating an

equivalent parallel termination voltage (V

TT

) of V

CCO

/2. HSTL_III_DCI provides on-chip

single termination powered from V

CCO

. HSTL_I_DCI and HSTL_III_DCI are intended to

be used in unidirectional links.

HSTL_ II, HSTL_ IV, HSTL_ II_18, HSTL_ IV_18

HSTL_II uses V

CCO

/2 as a parallel termination voltage (V

TT

). HSTL_IV uses V

CCO

as a

parallel termination voltage (V

TT

). HSTL_II and HSTL_IV are intended to be used in

bidirectional links.

Table 6-14: GTLP DC Voltage Specifications

Min Typ Max

V

CCO

–––

V

REF

= N × V

TT

(1)

0.88 1.0 1.12

V

TT

1.35 1.5 1.65

V

IH

= V

REF

+ 0.1 0.98 1.1 –

V

IL

= V

REF

– 0.1 – 0.9 1.02

V

OH

–––

V

OL

0.3 0.45 0.6

I

OH

at V

OH

(mA) – – –

I

OL

at V

OL

(mA) at 0.6V 36 – –

I

OL

at V

OL

(mA) at 0.3V – – 48

Notes:

1. N must be greater than or equal to 0.653 and less than or equal to 0.68.

Loading...

Loading...