210 www.xilinx.com Virtex-5 FPGA User Guide

UG190 (v5.0) June 19, 2009

Chapter 5: Configurable Logic Blocks (CLBs)

Slice Carry-Chain Timing Model and Parameters

Figure 5-24, page 199 illustrates a carry chain in a Virtex-5 FPGA slice. Some elements of

the slice have been omitted for clarity. Only the elements relevant to the timing paths

described in this section are shown.

Slice Carry-Chain Timing Parameters

Table 5-10 shows the slice carry-chain timing parameters for a majority of the paths in

Figure 5-24, page 199.

Slice Carry-Chain Timing Characteristics

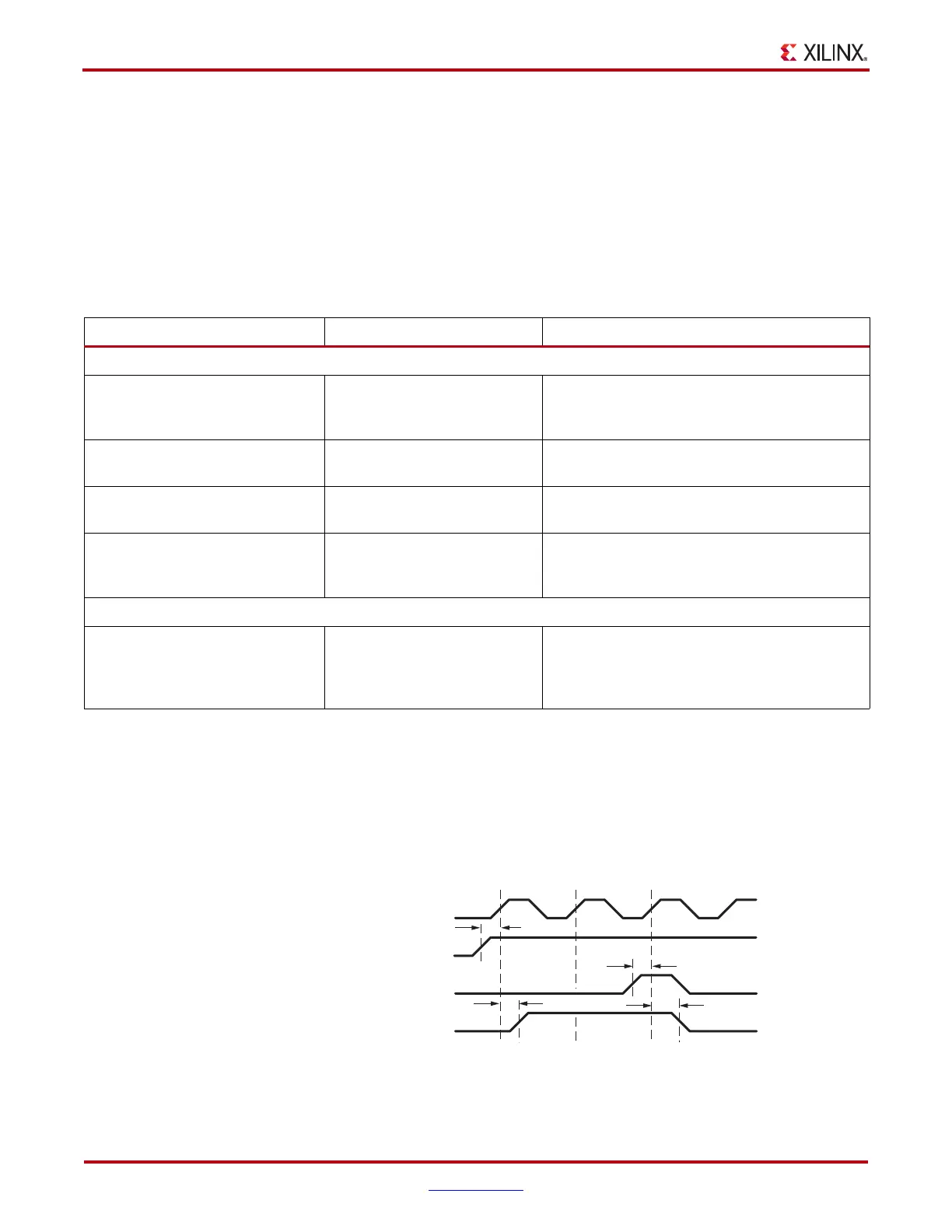

Figure 5-31 illustrates the timing characteristics of a slice carry chain implemented in a

Virtex-5 FPGA slice.

Table 5-10: Slice Carry-Chain Timing Parameters

Parameter Function Description

Sequential Delays for Slice LUT Configured as Carry Chain

T

AXCY

/T

BXCY

/T

CXCY

/T

DXCY

AX/BX/CX/DX input to

COUT output

Propagation delay from the AX/BX/CX/DX

inputs of the slice to the COUT output of the

slice.

T

BYP

CIN input to COUT output Propagation delay from the CIN input of the

slice to the COUT output of the slice.

T

OPCYA

/T

OPCYB

/T

OPCYC

/T

OPCYD

A/B/C/D input to COUT

output

Propagation delay from the A/B/C/D inputs of

the slice to the COUT output of the slice.

T

CINA

/T

CINB

/T

CINC

/T

CIND

A/B/C/D input to

AMUX/BMUX/CMUX/DMU

X output

Propagation delay from the A/B/C/D inputs of

the slice to AMUX/BMUX/CMUX/DMUX

output of the slice using XOR (sum).

Setup and Hold Times for a Slice LUT Configured as a Carry Chain

(1)

T

CINCK

/T

CKCIN

CIN Data inputs Time before the CLK that data from the CIN

input of the slice must be stable at the D input of

the slice sequential elements (configured as a

flip-flop).

Notes:

1. T

XXCK

= Setup Time (before clock edge), and T

CKXX

= Hold Time (after clock edge).

X-Ref Target - Figure 5-31

Figure 5-31: Slice Carry-Chain Timing Characteristics

ug190_5_31_050506

T

CINCK

123

CLK

C

IN

( DATA)

SR (RESET)

AQ/BQ/CQ/DQ

(OUT)

T

CKO

T

SRCK

T

CKO

Loading...

Loading...