344 www.xilinx.com Virtex-5 FPGA User Guide

UG190 (v5.0) June 19, 2009

Chapter 7: SelectIO Logic Resources

Instantiating Multiple IDELAYCTRLs Without LOC Constraints

Instantiating multiple IDELAYCTRL instances without LOC properties is prohibited. If

this occurs, an error is issued by the implementation tools.

OLOGIC Resources

OLOGIC consists of two major blocks, one to configure the output data path and the other

to configure the 3-state control path. These two blocks have a common clock (CLK) but

different enable signals, OCE and TCE. Both have asynchronous and synchronous set and

reset (SR and REV signals) controlled by an independent SRVAL attribute as described in

the Table 7-1 and Table 7-2.

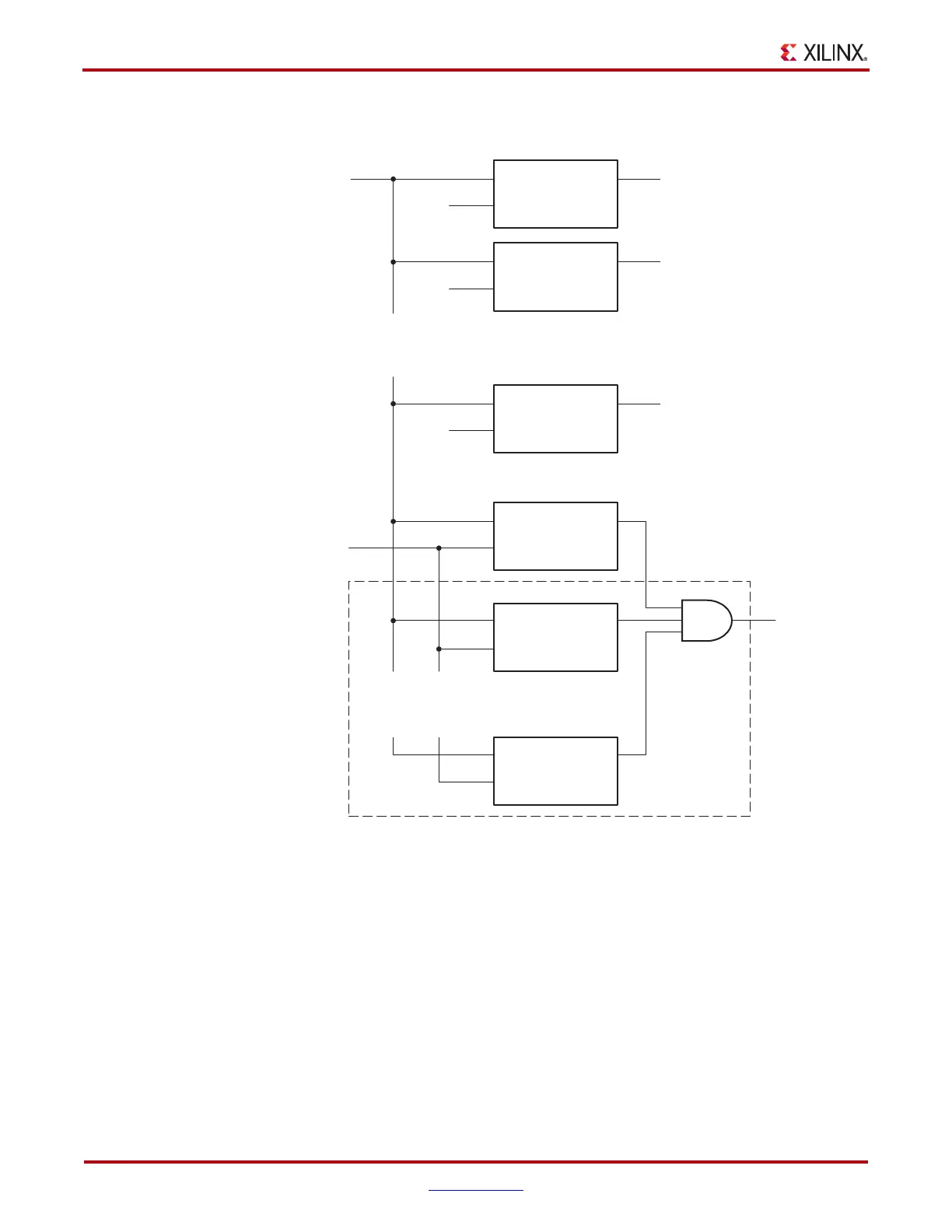

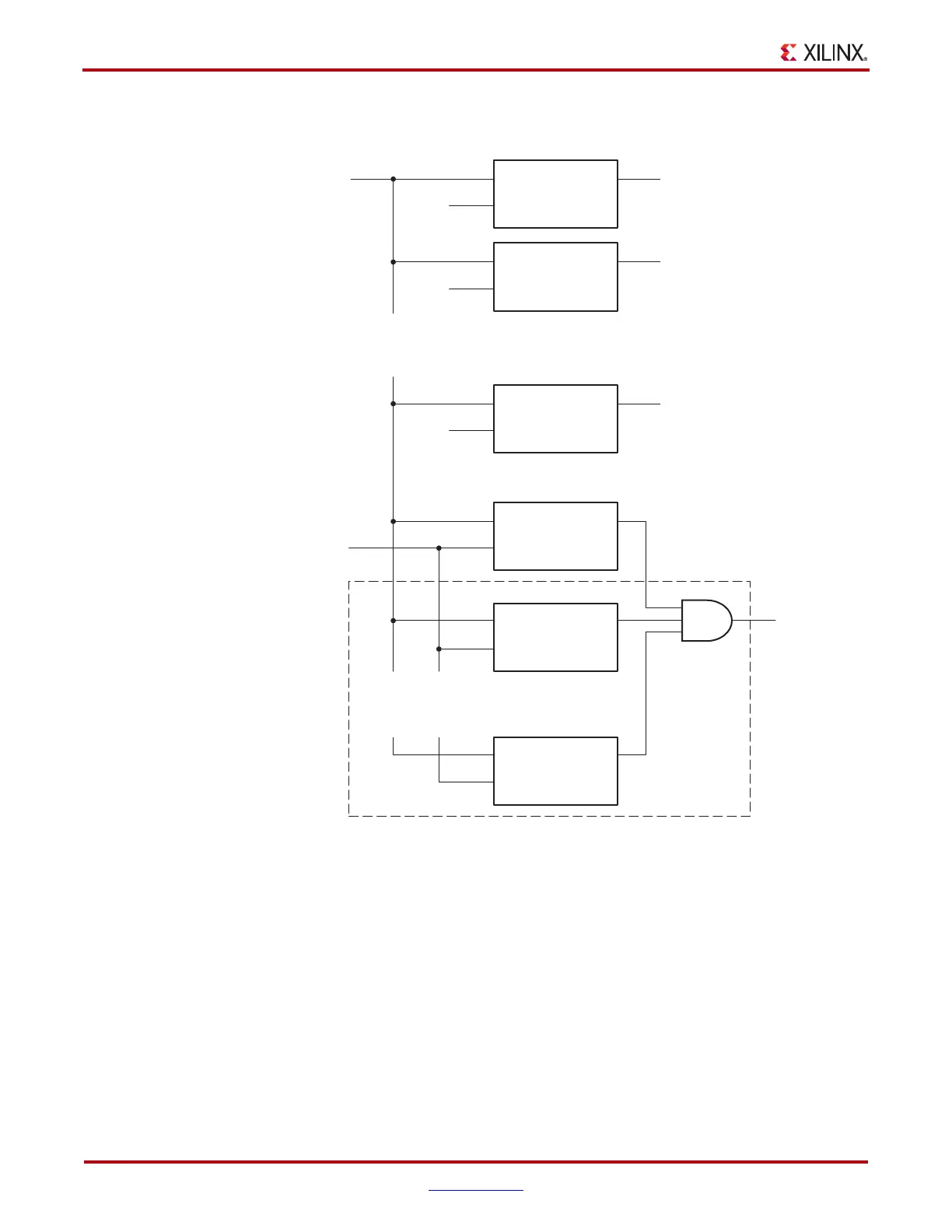

X-Ref Target - Figure 7-21

Figure 7-21: Mixed Instantiation of IDELAYCTRL Elements

REFCLK

RST_NOLOC

rst_n

RDY_NOLOC

rdy_n

Instantiated without

LOC Constraint

Instantiated with

LOC Constraint

REFCLK RDY

RST

IDELAYCTRL_noloc

IDELAYCTRL_noloc

IDELAYCTRL_noloc

REFCLK RDY

RST

REFCLK RDY

RST

ug190_7_16_041306

REFCLK RDY

RST

IDELAYCTRL_n

rst_2

rdy_2

REFCLK RDY

RST

IDELAYCTRL_2

rst_1

rdy_1

REFCLK RDY

RST

IDELAYCTRL_1

.

.

.

.

.

.

Replicated for

all IDELAYCTRL

sites

.

.

.

Auto-generated

by mapper tool

.

.

.

.

.

.

.

.

.

Loading...

Loading...