110 www.xilinx.com Virtex-5 FPGA User Guide

UG190 (v5.0) June 19, 2009

Chapter 3: Phase-Locked Loops (PLLs)

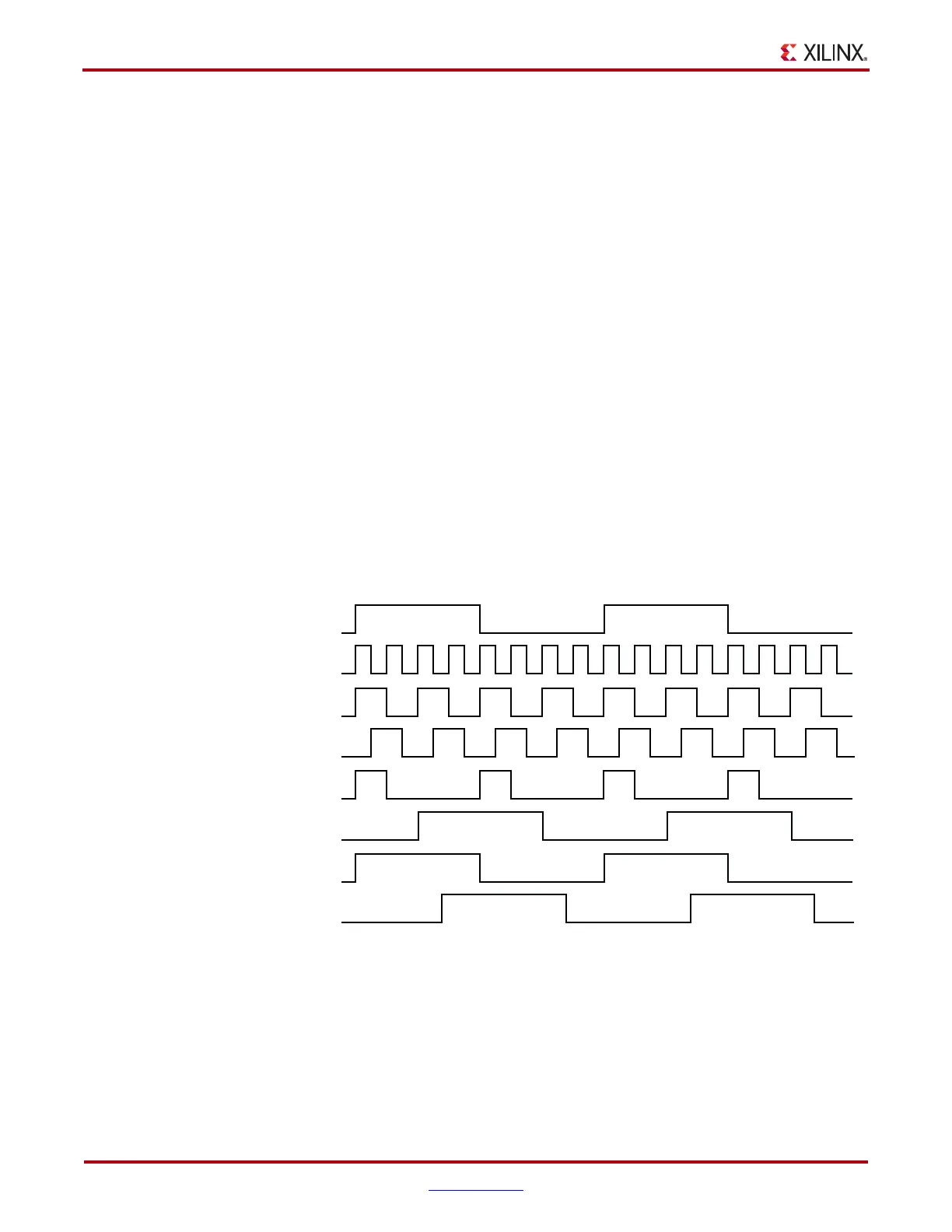

PLL Application Example

The following PLL attribute settings result in a wide variety of synthesized clocks:

CLKOUT0_PHASE = 0;

CLKOUT0_DUTY_CYCLE = 0.5;

CLKOUT0_DIVIDE = 2;

CLKOUT1_PHASE = 90;

CLKOUT1_DUTY_CYCLE = 0.5;

CLKOUT1_DIVIDE = 2;

CLKOUT2_PHASE = 0;

CLKOUT2_DUTY_CYCLE = 0.25;

CLKOUT2_DIVIDE = 4;

CLKOUT3_PHASE = 90;

CLKOUT3_DUTY_CYCLE = 0.5;

CLKOUT3_DIVIDE = 8;

CLKOUT4_PHASE = 0;

CLKOUT4_DUTY_CYCLE = 0.5;

CLKOUT4_DIVIDE = 8;

CLKOUT5_PHASE = 135;

CLKOUT5_DUTY_CYCLE = 0.5;

CLKOUT5_DIVIDE = 8;

CLKFBOUT_PHASE = 0;

CLKFBOUT_MULT = 8;

DIVCLK_DIVIDE = 1;

CLKIN1_PERIOD = 10.0;

Figure 3-16 displays the resulting waveforms.

X-Ref Target - Figure 3-16

Figure 3-16: Example Waveform

REFCLK

VCOCLK

CLKOUT0

CLKOUT1

CLKOUT2

CLKOUT3

CLKOUT4

CLKOUT5

UG190_3_19_032506

Loading...

Loading...