164 www.xilinx.com Virtex-5 FPGA User Guide

UG190 (v5.0) June 19, 2009

Chapter 4: Block RAM

Block RAM and FIFO ECC Attributes

In addition to the built-in registers in the decode and correct logic, the RAMB36SDP

primitive allows the use of optional pipeline registers controlled by the DO_REG attribute

to produce higher performance with one additional latency. Table 4-23 and Table 4-24 list

the block RAM and FIFO ECC attributes.

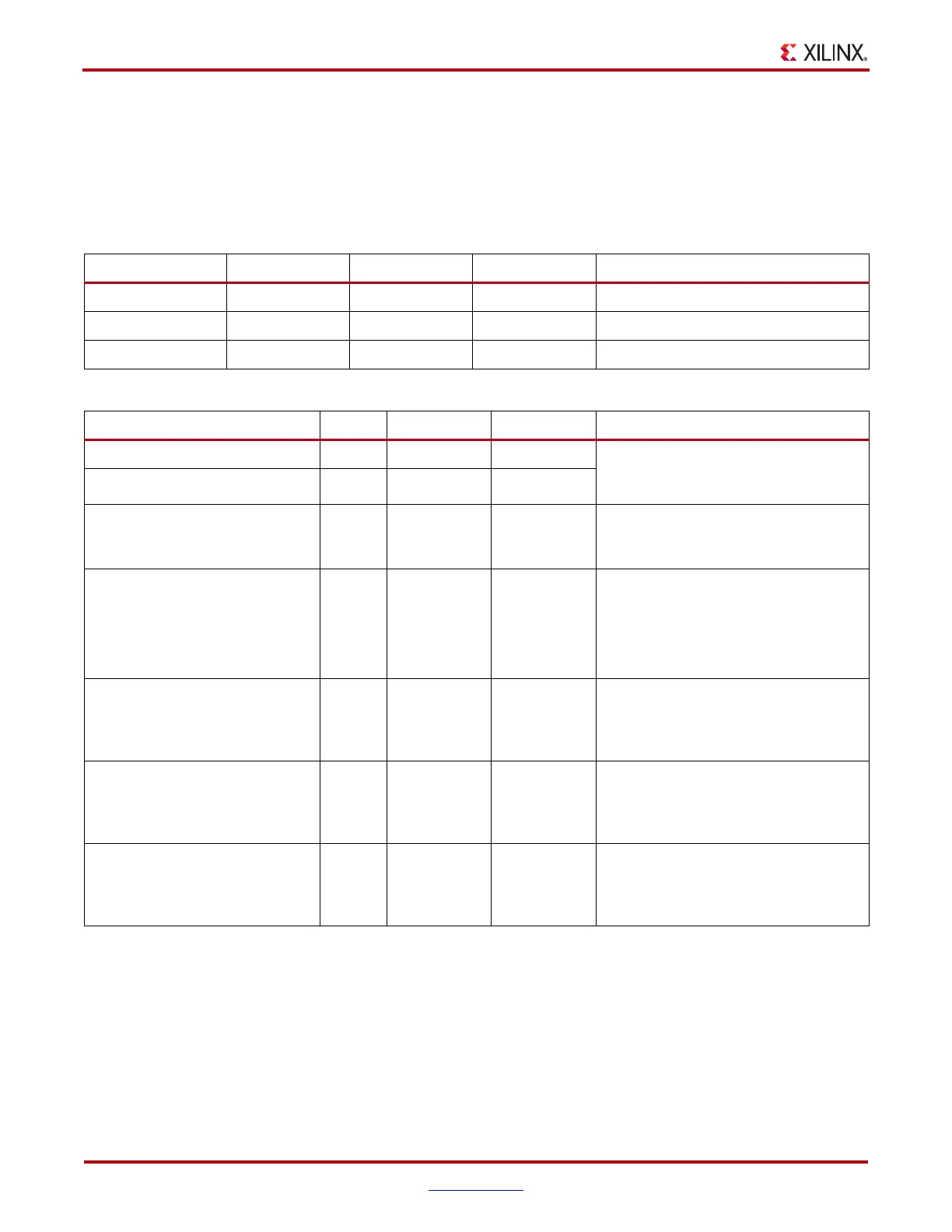

Table 4-23: Block RAM (RAMB36SDP) Attributes

Attribute Name Type Values Default Notes

EN_ECC_WRITE Boolean TRUE, FALSE FALSE Set to TRUE to enable ECC encoder.

EN_ECC_READ Boolean TRUE, FALSE FALSE Set to TRUE to enable ECC decoder.

DO_REG 1-bit Binary 0, 1 0 Enables register mode or latch mode.

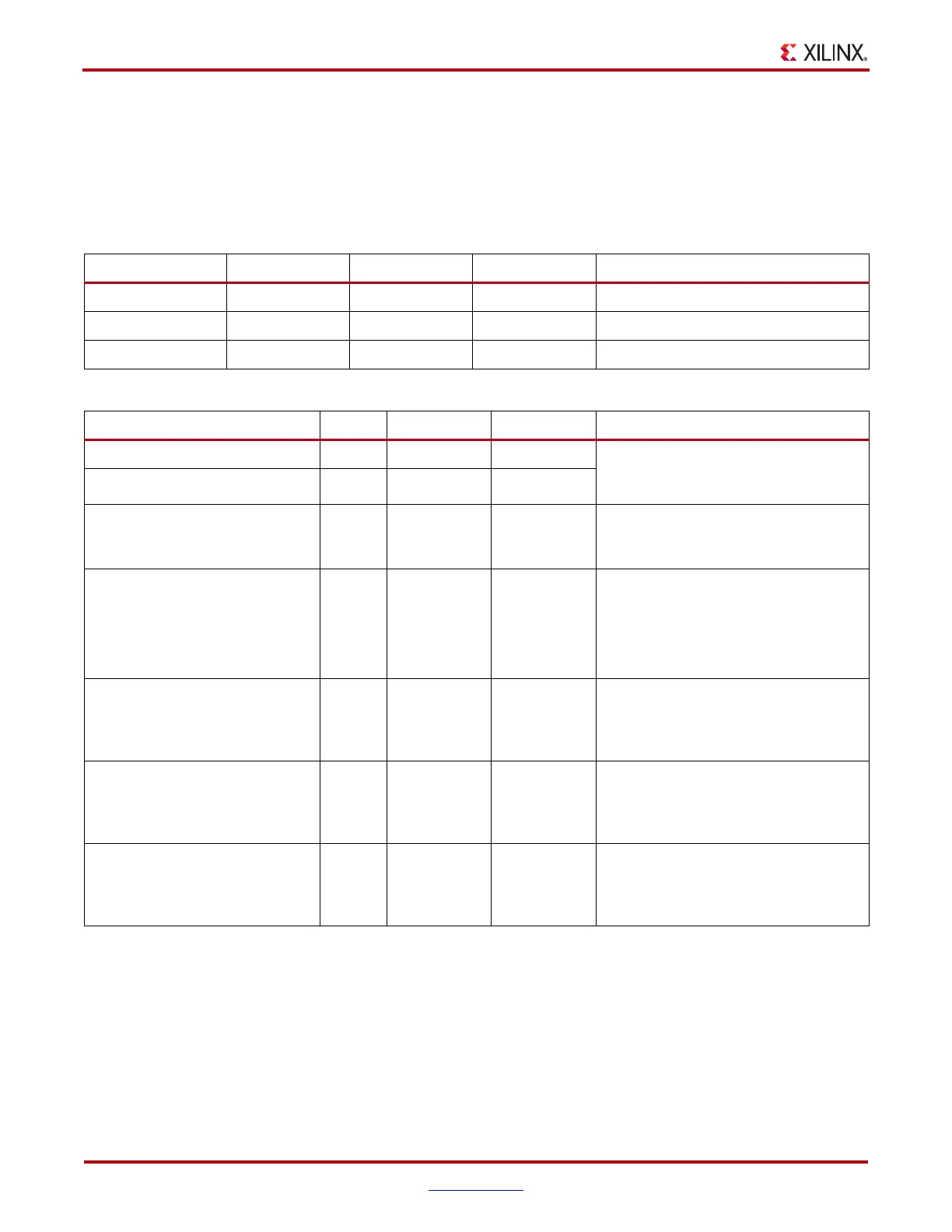

Table 4-24: FIFO (FIFO36_72) Attributes

Attribute Name Type Values Default Notes

EN_ECC_WRITE Boolean TRUE, FALSE FALSE Both attributes must be set to TRUE to

enable ECC functionality in a

FIFO36_72.

EN_ECC_READ

Boolean TRUE, FALSE FALSE

DO_REG

1-bit

Binary

0, 1 1

Enables register mode or latch mode. See

Table 4-17 for details on multirate and

synchronous FIFOs.

EN_SYN

Boolean TRUE, FALSE FALSE

When set to TRUE, ties WRCLK and

RDCLK together.

When set to TRUE, FWFT must be

FALSE.

When set to FALSE, DO_REG must be 1.

ALMOST_EMPTY_OFFSET

9-bit

Hex

See Table 4-19 See Table 4-19

Setting determines the difference

between EMPTY and ALMOST_EMPTY

conditions. Must be set using

hexadecimal notation.

ALMOST_FULL_OFFSET

9-bit

Hex

See Table 4-19 See Table 4-19

Setting determines the difference

between FULL and ALMOST_FULL

conditions. Must be set using

hexadecimal notation.

FIRST_WORD_FALL_THROUGH

Boolean TRUE, FALSE FALSE

When set to TRUE, the first word written

into the empty FIFO36_72 appears at the

FIFO36_72 output without RDEN

asserted.

Loading...

Loading...