Virtex-5 FPGA User Guide www.xilinx.com 163

UG190 (v5.0) June 19, 2009

Built-in Error Correction

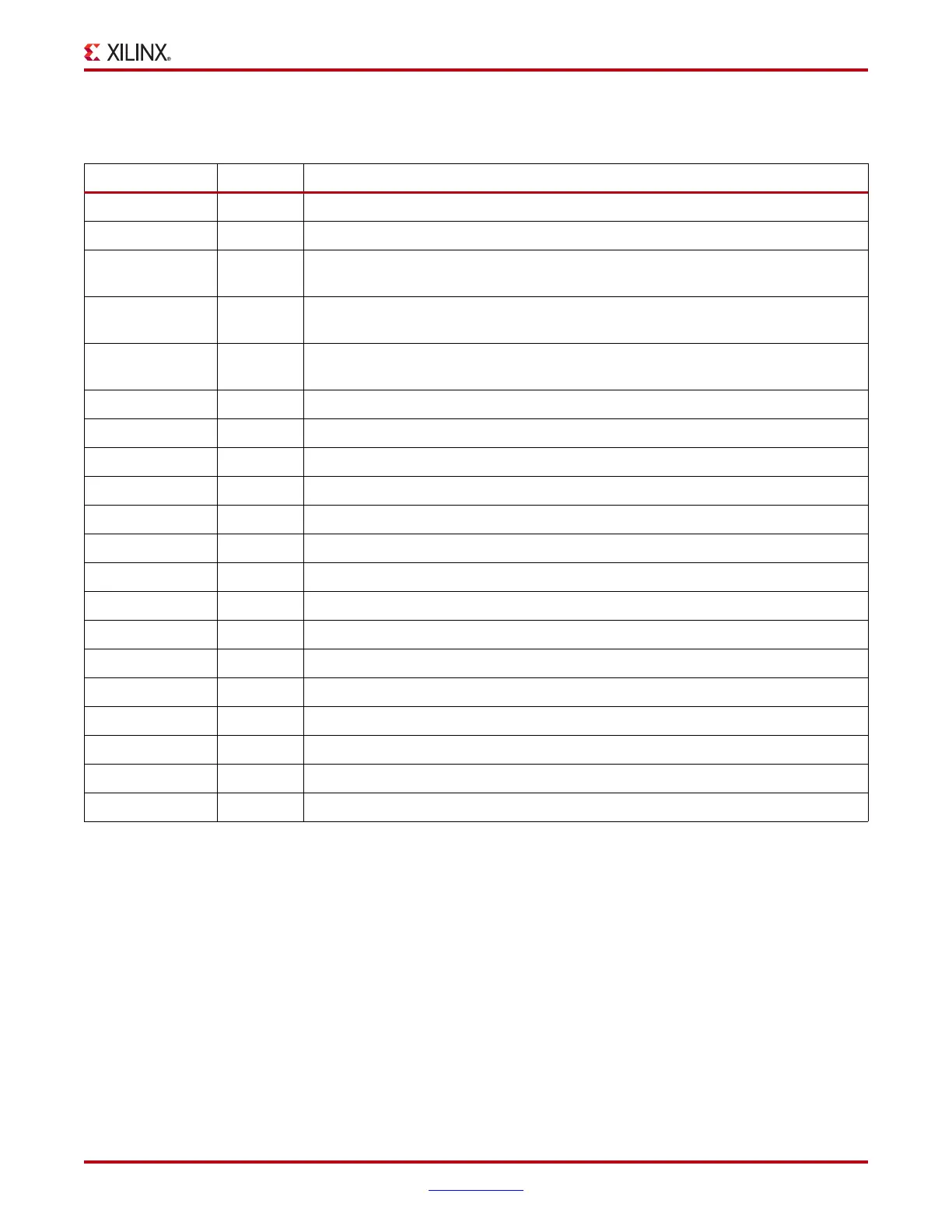

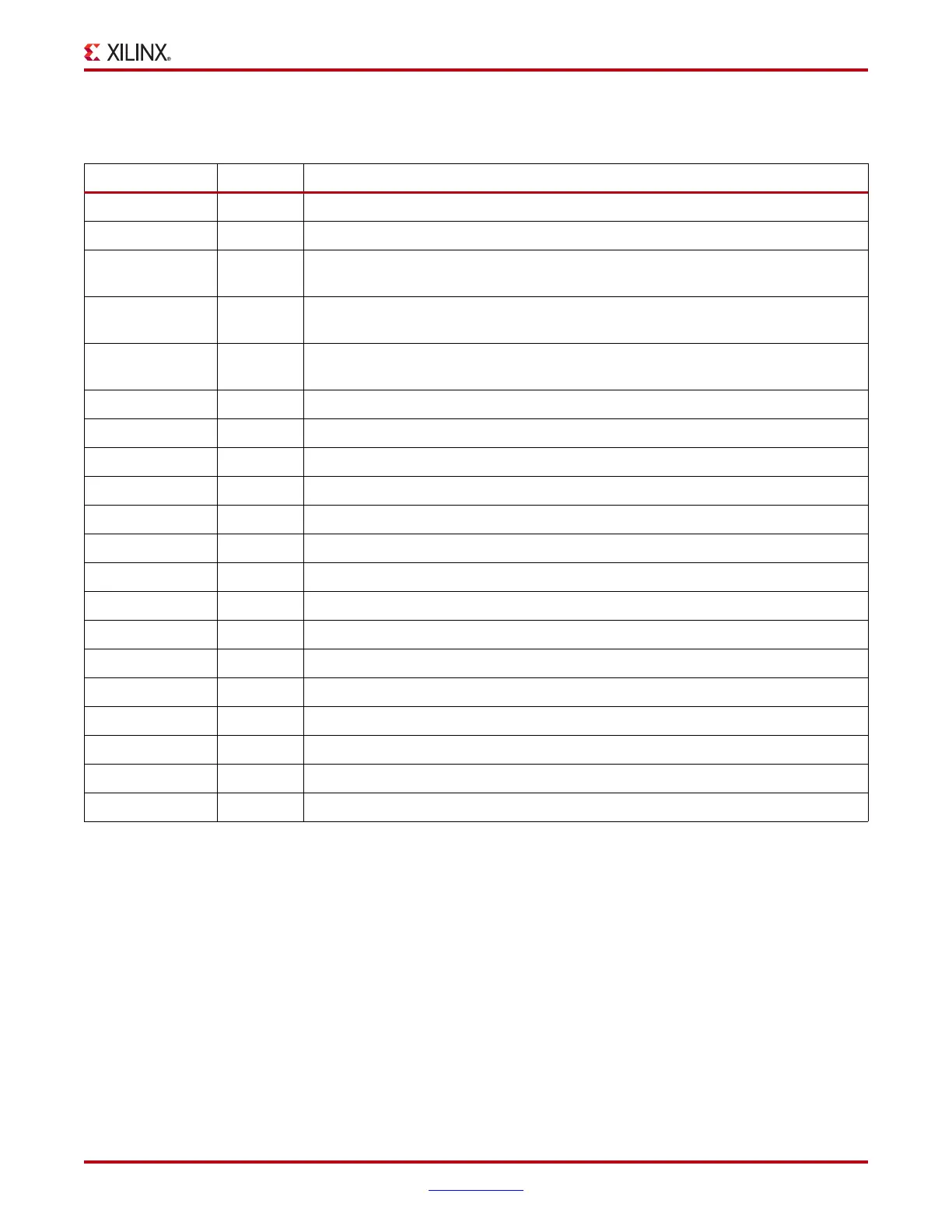

Table 4-22 lists and describes the FIFO ECC I/O port names.

Table 4-22: FIFO ECC Port Names and Descriptions

Port Name Direction Signal Description

DI[63:0] Input Data input bus.

DIP[7:0] Input Data input parity bus. Not used when standard mode is used.

WREN Input Write enable. When WREN = 1, data will be written into memory. When WREN = 0,

write is disabled

RDEN Input Read enable. When RDEN = 1, data will be read from memory. When RDEN = 0, read

is disabled.

RST Input Asynchronous reset of FIFO counter and flags. Reset must be asserted for three clock

cycles. Reset does not affect DO or ECC signals.

WRCLK Input Clock for write operations.

RDCLK Input Clock for read operations.

DO[63:0] Output Data output bus.

DOP[7:0] Output Data output parity bus.

SBITERR

(1)

Output Single-bit error status.

DBITERR

(1)

Output Double-bit error status.

ECCPARITY[7:0] Output ECC encoder output bus.

FULL Output FIFO FULL flag.

ALMOSTFULL Output FIFO ALMOSTFULL flag.

EMPTY Output FIFO EMPTY flag.

ALMOSTEMPTY Output FIFO ALMOSTEMPTY flag.

RDCOUNT Output The FIFO data read pointer.

WRCOUNT Output The FIFO data write pointer.

WRERR Output When the FIFO is full, any additional write operation generates an error flag.

RDERR Output When the FIFO is empty, any additional read operation generates an error flag.

Notes:

1. Hamming code implemented in the FIFO ECC logic detects one of three conditions: no detectable error, single-bit error detected and

corrected on DO (but not corrected in the memory), and double-bit error detected without correction. SBITERR and DBITERR

indicate these three conditions.

Loading...

Loading...