UG190 (v5.0) June 19, 2009 www.xilinx.com Virtex-5 FPGA User Guide

Revision History

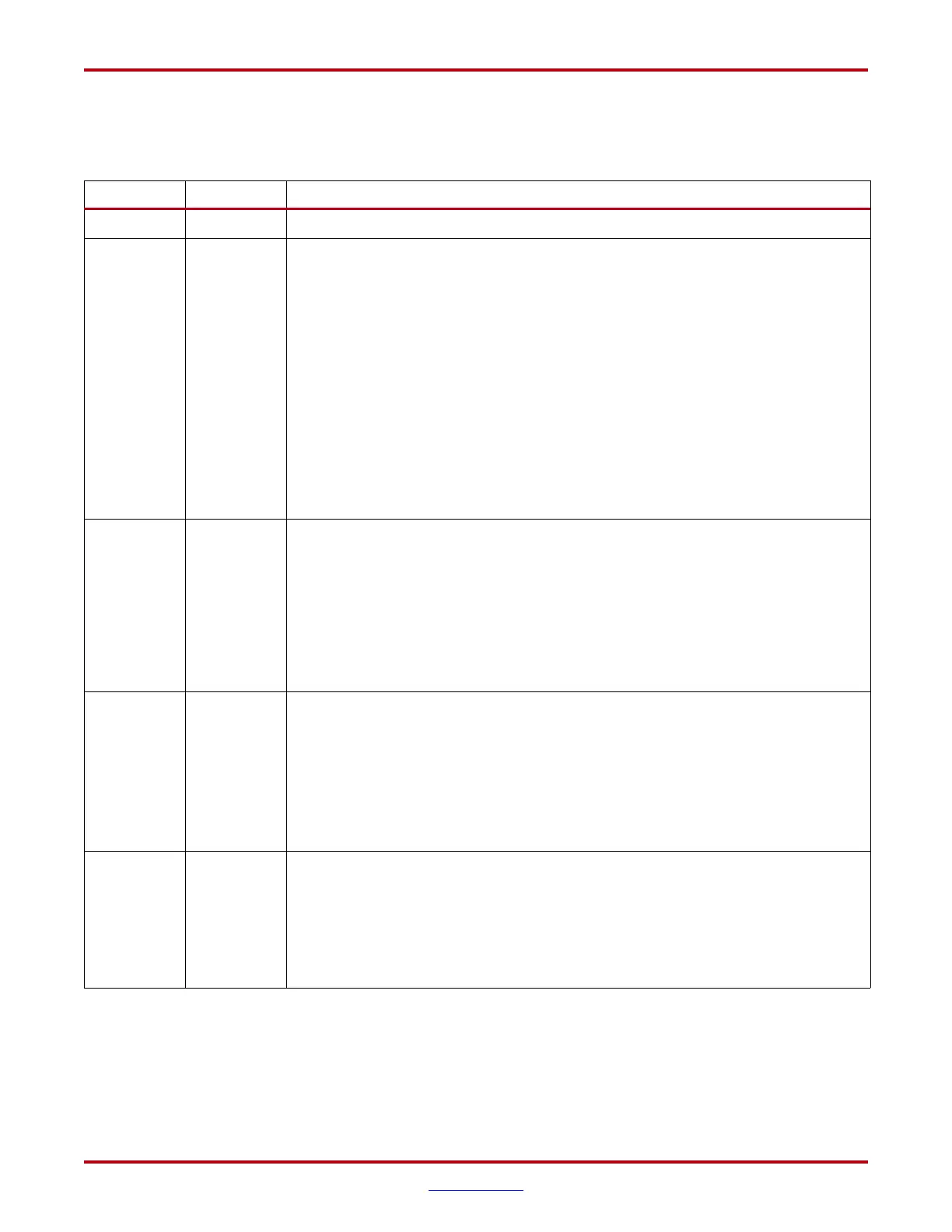

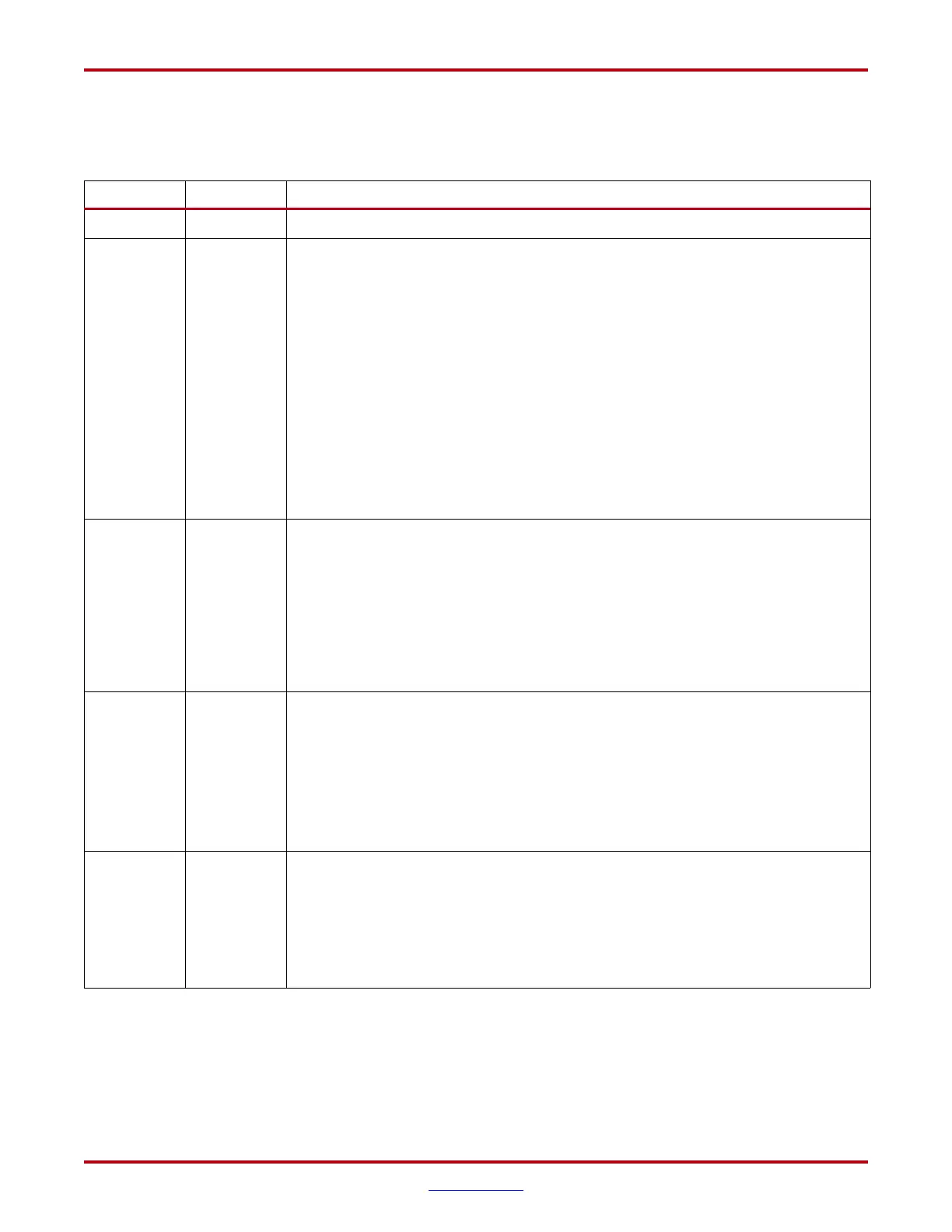

The following table shows the revision history for this document.

Date Version Revision

04/14/06 1.0 Initial Xilinx release.

05/12/06 1.1 Minor typographical edits and clarifications.

Chapter 1: Revised Figure 1-21.

Chapter 2: Revised Figure 2-2 and Figure 2-4. Removed reference to a DCM_PS

primitive. Removed outdated clocking wizard section page 83.

Chapter 3: Revised Figure 3-1, Figure 3-2, Table 3-2, Table 3-4, Figure 3-9, Equation 3-8,

and Figure 3-12. Added “PLL in Virtex-4 FPGA PMCD Legacy Mode” section.

Chapter 4: Added a note to Table 4-5, page 124. Clarified the RAMB36 port mapping

design rules on page 132.

Chapter 5: Added Figure 5-7 and Figure 5-11, revised Figure 5-32 for clarity.

Chapter 6: Updated “Simultaneous Switching Output Limits” section.

Chapter 7: Revised “ILOGIC Resources,” page 318 including Figure 7-1. Revised

Table 7-3.

Chapter 8: Revised Table 8-1.

7/19/06 1.2 Chapter 1: Revised “Global Clock Buffers,” page 27 to clarify single-ended clock pins.

Changed the P and N I/O designations in Figure 1-19.

Chapter 4: Added “Block RAM SSR in Register Mode,” page 133 and “FIFO Architecture:

a Top-Level View,” page 142. Revised the FIFO operations “Reset,” page 144 description.

Chapter 6: Minor clarification edits. Changed to N/A from unused in Table 6-36,

Table 6-37, and Table 6-38.

Chapter 7: Minor edits to clarify IODELAY in this chapter.

Chapter 8: Small clarifications in “ISERDES_NODELAY Ports” on page 355.

9/06/06 2.0 Added the LXT platform devices throughout document.

Chapter 1: Revised Figure 1-22, page 45. Updated “Clock Capable I/O” on page 40.

Chapter 2: Updated “Output Clocks” on page 65.

Chapter 4: Clarified the rules regarding FULL and EMPTY flags on page 139.

Chapter 5: Revised “Storage Elements” on page 178.

Chapter 6: “Differential Termination Attribute” on page 237 is updated for the latest

syntax and settings. Replaced the link to the SSO calculator.

10/12/06 2.1 Added System Monitor User Guide reference in the Preface.

Added XC5VLX85T to Table 1-5, Table 2-1, and Table 5-2.

Chapter 3: Revised Figure 3-1.

Chapter 4: Added cascade to Table 4-7, page 126. Revised ADDR in Figure 4-9, page 124.

Removed scrub mode in “Built-in Error Correction” section.

Chapter 5: Revised Figure 5-22, page 197.

Loading...

Loading...