Virtex-5 FPGA User Guide www.xilinx.com 39

UG190 (v5.0) June 19, 2009

Global Clocking Resources

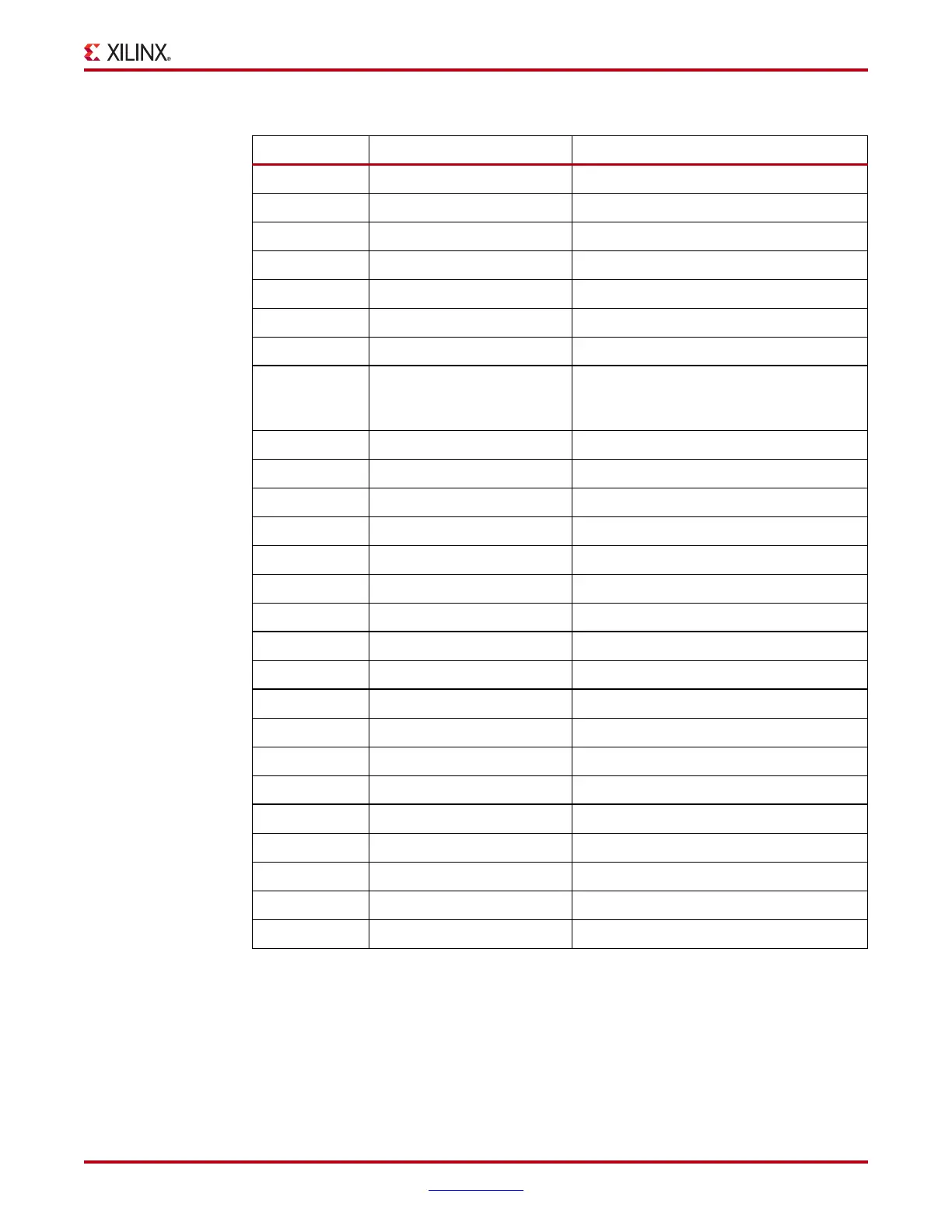

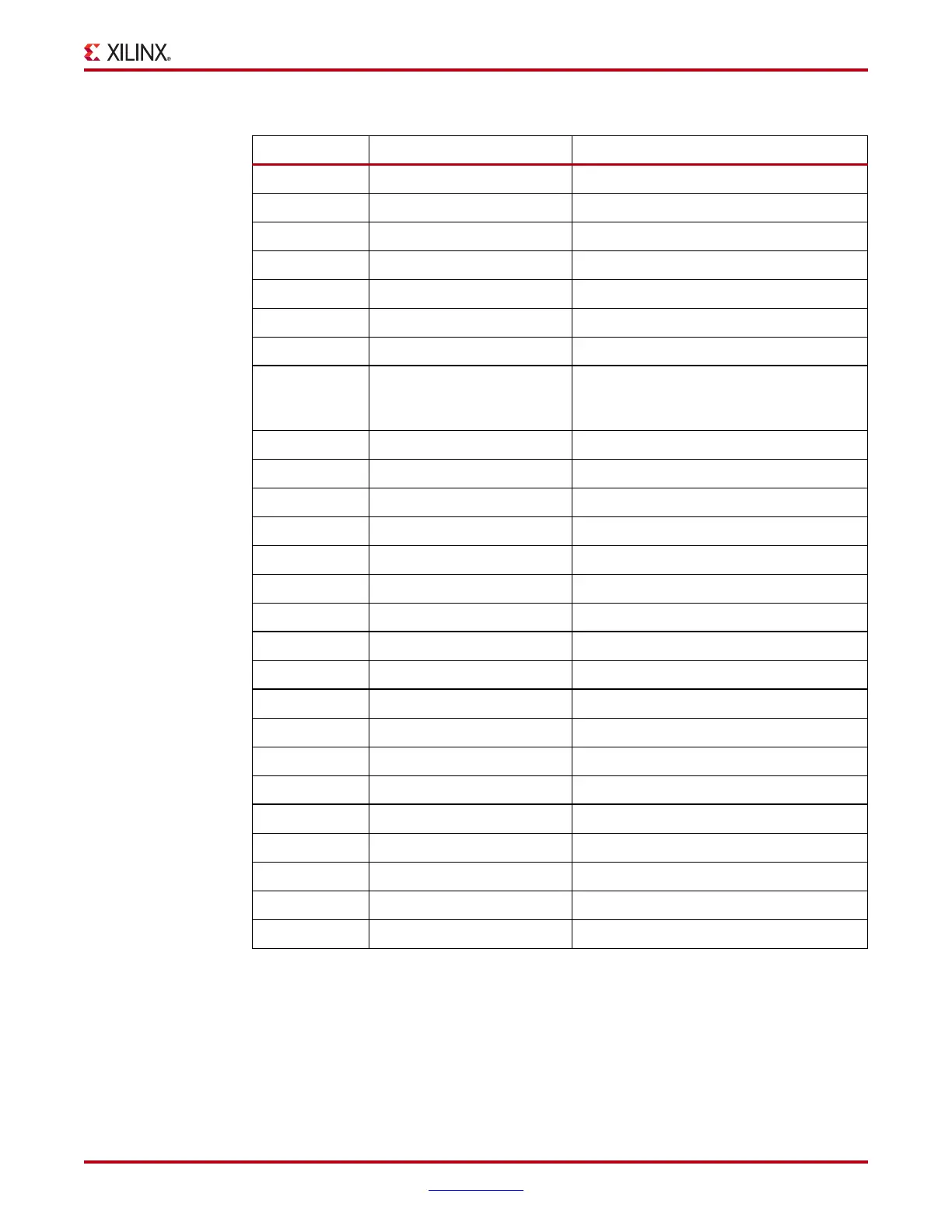

Table 1-5: Virtex-5 FPGA Clock Regions

Device Number of Clock Regions Notes

XC5VLX30 8

XC5VLX50 12

XC5VLX85 12

XC5VLX110 16

XC5VLX155 16

XC5VLX220 16

XC5VLX330 24

XC5VLX20T 6 There are 3 regions on each side of the

device. There are no BUFRs on the right

side of this device.

XC5VLX30T 8

XC5VLX50T 12

XC5VLX85T 12

XC5VLX110T 16

XC5VLX155T 16

XC5VLX220T 16

XC5VLX330T 24

XC5VTX150T 20

XC5VTX240T 24

XC5VSX35T 8

XC5VSX50T 12

XC5VSX95T 16

XC5VSX240T 24

XC5VFX30T 8

XC5VFX70T 16

XC5VFX100T 16

XC5VFX130T 20

XC5VFX200T 24

Loading...

Loading...