58 www.xilinx.com Virtex-5 FPGA User Guide

UG190 (v5.0) June 19, 2009

Chapter 2: Clock Management Technology

DCM Attributes

A handful of DCM attributes govern the DCM functionality. Table 2-6 summarizes all the

applicable DCM attributes. This section provides a detailed description of each attribute.

For more information on applying these attributes in UCF, VHDL, or Verilog code, refer to

the Constraints Guide at:

http://www.support.xilinx.com/support/software_manuals.htm

.

CLKDV_DIVIDE Attribute

The CLKDV_DIVIDE attribute controls the CLKDV frequency. The source clock frequency

is divided by the value of this attribute. The possible values for CLKDV_DIVIDE are: 1.5,

2, 2.5, 3, 3.5, 4, 4.5, 5, 5.5, 6, 6.5, 7, 7.5, 8, 9, 10, 11, 12, 13, 14, 15, or 16. The default value is 2.

In the low frequency mode, any CLKDV_DIVIDE value produces a CLKDV output with a

50/50 duty-cycle. In the high frequency mode, the CLKDV_DIVIDE value must be set to

an integer value to produce a CLKDV output with a 50/50 duty-cycle. For non-integer

CLKDV_DIVIDE values, the CLKDV output duty cycle is shown in Table 2-5.

CLKFX_MULTIPLY and CLKFX_DIVIDE Attribute

The CLKFX_MULTIPLY attribute sets the multiply value (M) of the CLKFX output. The

CLKFX_DIVIDE attribute sets the divisor (D) value of the CLKFX output. Both control the

CLKFX output making the CLKFX frequency equal the effective CLKIN (source clock)

frequency multiplied by M/D. The possible values for M are any integer from two to 33.

The possible values for D are any integer from 1 to 32. The default settings are M = 4 and

D=1.

CLKIN_PERIOD Attribute

The CLKIN_PERIOD attribute specifies the source clock period (in nanoseconds). The

default value is 0.0 ns. Setting this attribute to the input period values produces the best

results.

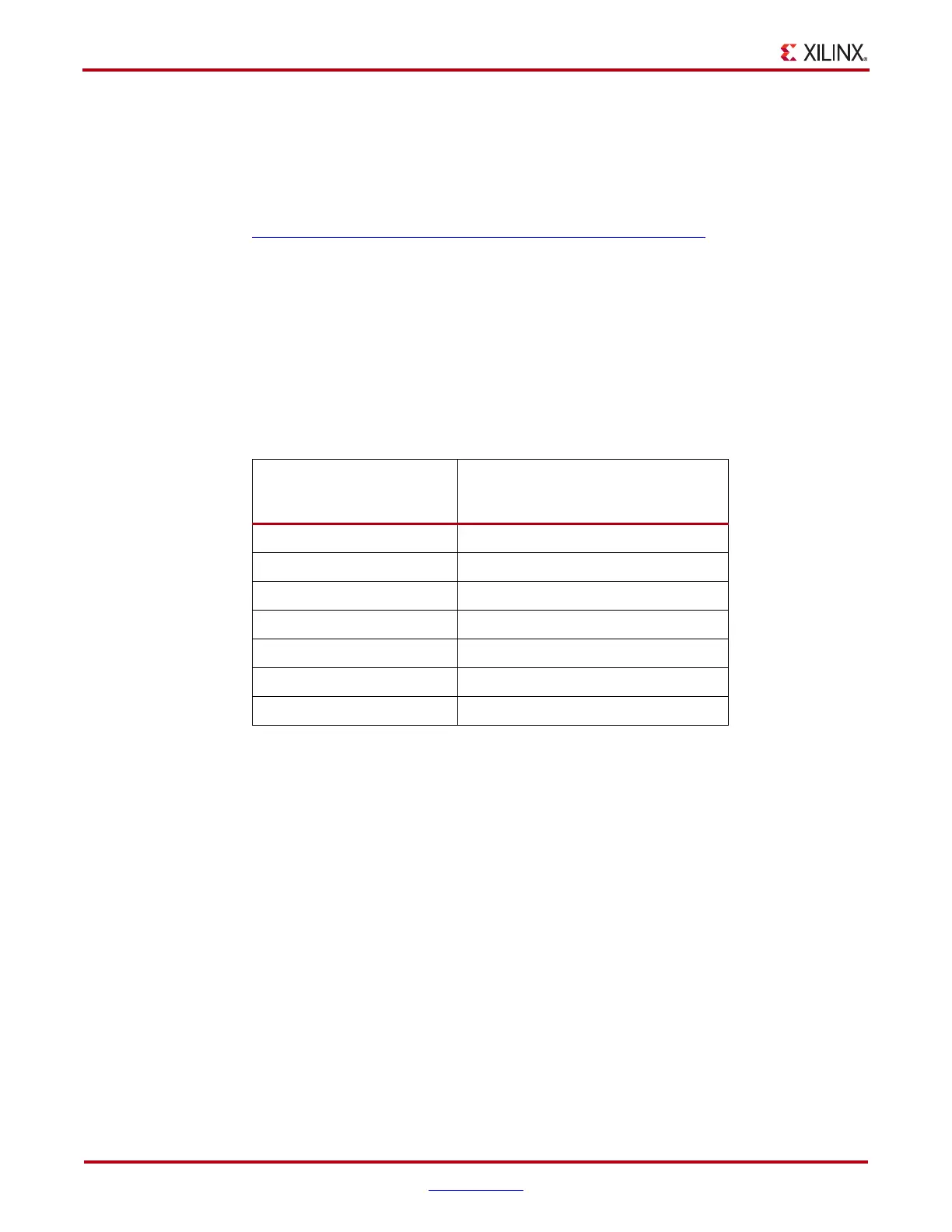

Table 2-5: Non-Integer CLKDV_DIVIDE

CLKDV_DIVIDE Value

CLKDV Duty Cycle in

High Frequency Mode

(High Pulse/Low Pulse Value)

1.5 1/3

2.5 2/5

3.5 3/7

4.5 4/9

5.5 5/11

6.5 6/13

7.5 7/15

Loading...

Loading...