Virtex-5 FPGA User Guide www.xilinx.com 45

UG190 (v5.0) June 19, 2009

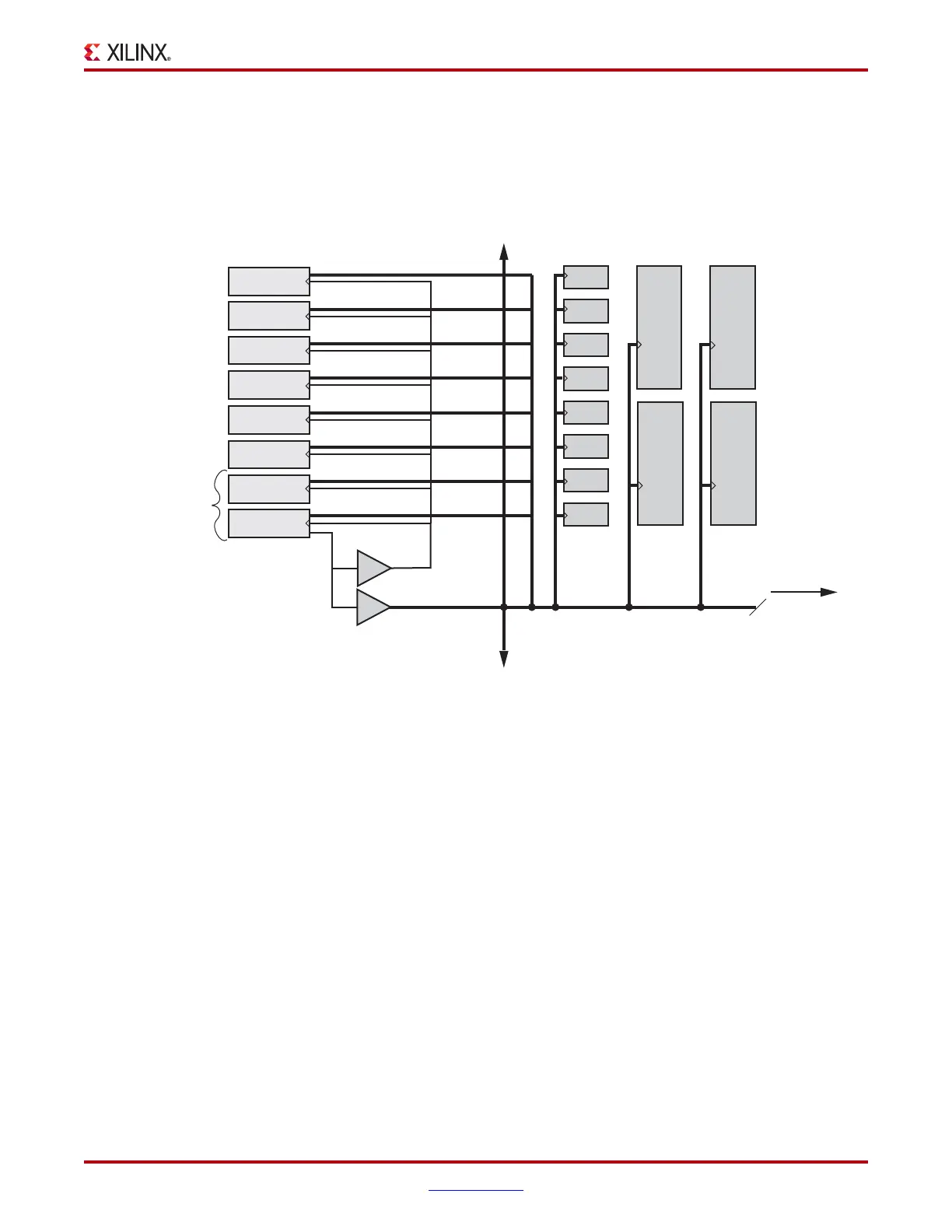

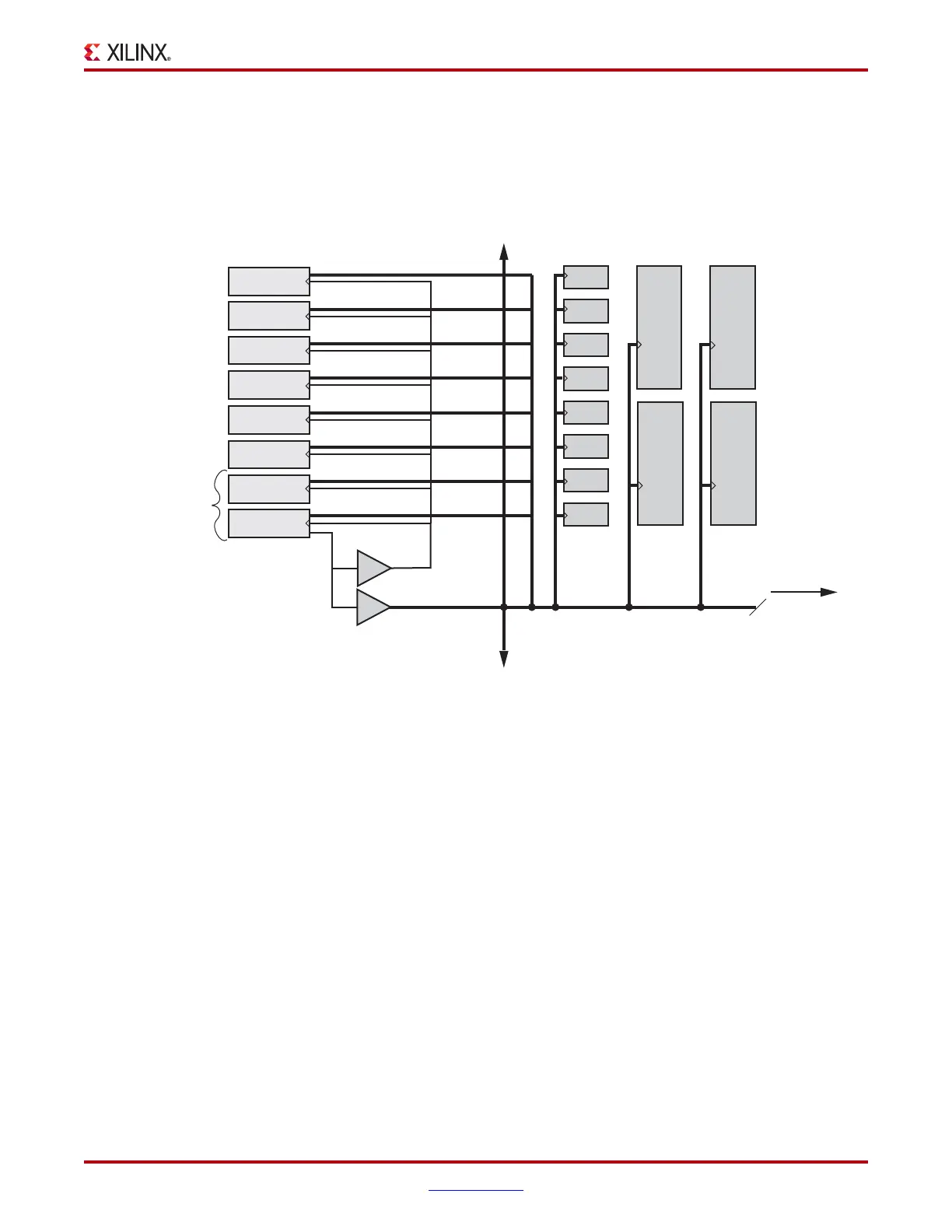

Regional Clocking Resources

BUFR Use Models

BUFRs are ideal for source-synchronous applications requiring clock domain crossing or

serial-to-parallel conversion. Unlike BUFIOs, BUFRs are capable of clocking logic

resources in the FPGAs other than the IOBs. Figure 1-22 is a BUFR design example.

X-Ref Target - Figure 1-22

Figure 1-22: BUFR Driving Various Logic Resources

UG190_c1_22_022609

CLBs

CLBs

CLBs

CLBs

CLBs

CLBs

CLBs

CLBs

Block

RAM

Block

RAM

DSP

Tile

DSP

Tile

BUFR

To Region

Above

To Center

of Die

To Region

Below

I/O Tile

I/O Tile

I/O Tile

I/O Tile

I/O Tile

I/O Tile

I/O Tile

I/O Tile

BUFIO

Clock Capable I/O

Loading...

Loading...