84 www.xilinx.com Virtex-5 FPGA User Guide

UG190 (v5.0) June 19, 2009

Chapter 2: Clock Management Technology

DCM Timing Models

The following timing diagrams describe the behavior of the DCM clock outputs under four

different conditions:

1. Reset/Lock

2. Fixed-Phase Shifting

3. Variable-Phase Shifting

4. Status Flags

Reset/Lock

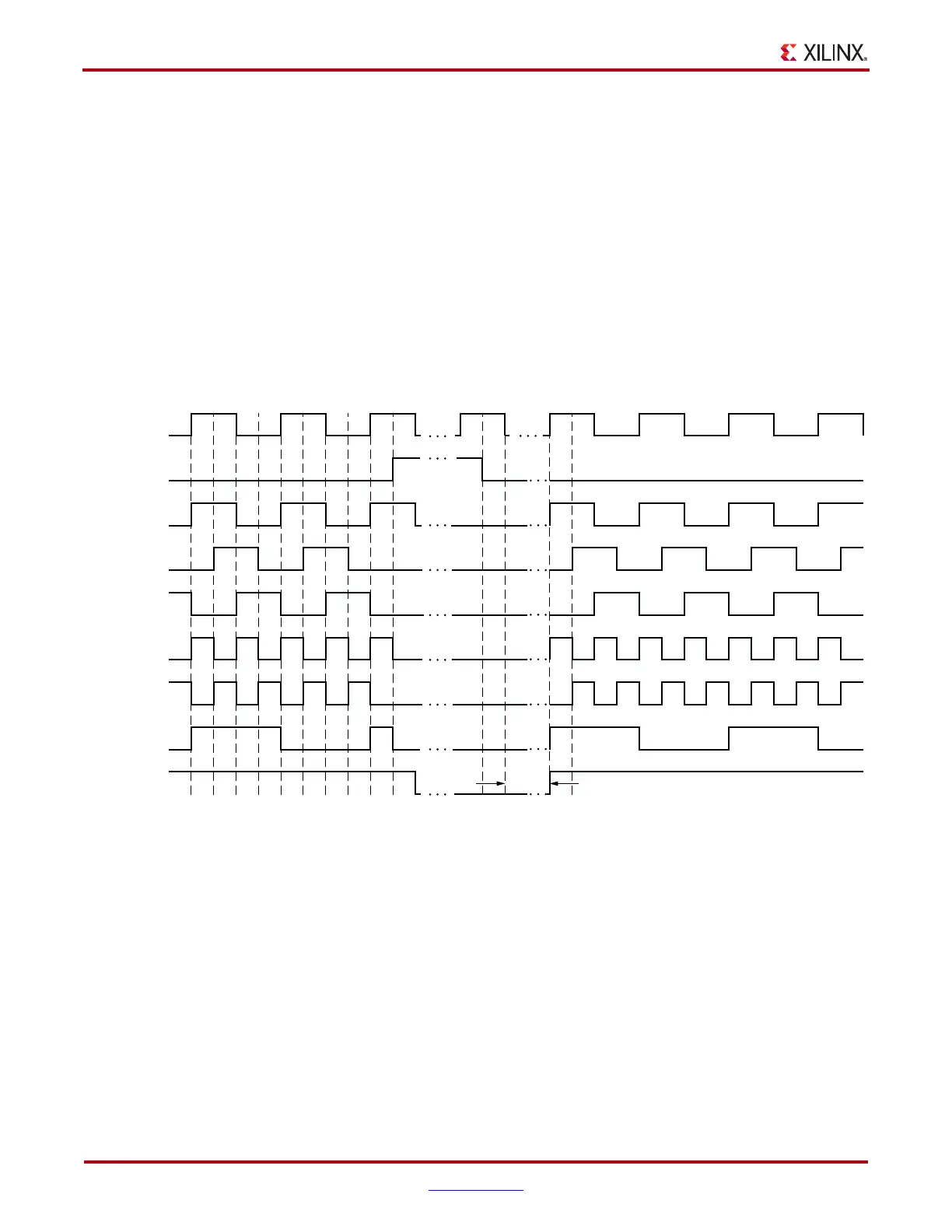

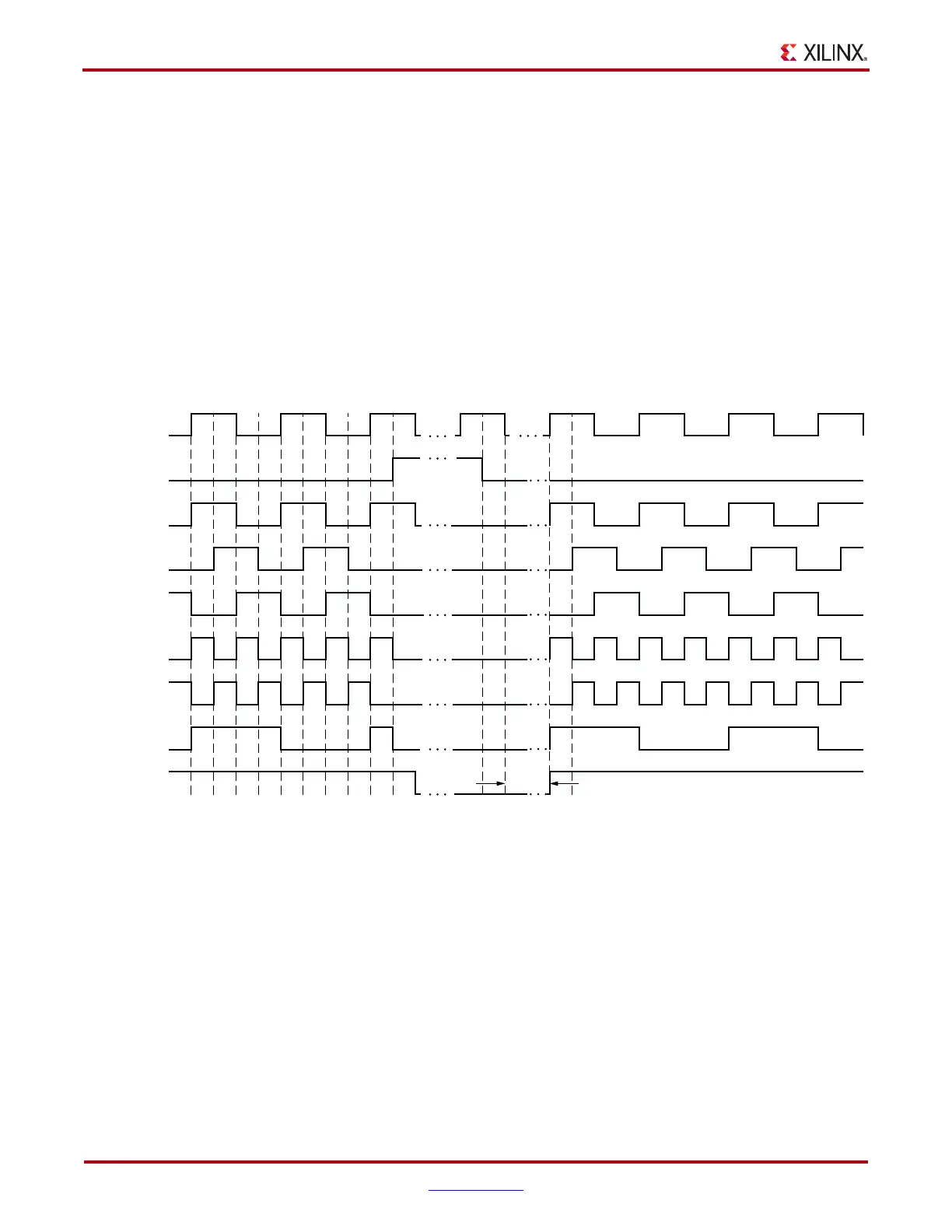

In Figure 2-17, the DCM is already locked. After the reset signal is applied, all output

clocks are stabilized to the desired values, and the LOCKED signal is asserted.

• Prior to Clock Event 1

Prior to clock event 1, the DCM is locked. All clock outputs are in phase with the

correct frequency and behavior.

• Clock Event 1

Some time after clock event 1 the reset signal is asserted at the (RST) pin. While reset is

asserted, all clock outputs become a logic zero. The reset signal is an asynchronous

reset. Note: the diagram is not shown to scale. For the DCM to operate properly, the

reset signal must be asserted for at least three CLKIN periods.

• Clock Event 2

Clock event 2 occurs a few cycles after reset is asserted and deasserted. At clock event

2, the lock process begins. At time LOCK_DLL, after clock event 2, if no fixed phase

shift was selected then all clock outputs are stable and in phase. LOCKED is also

asserted to signal completion.

X-Ref Target - Figure 2-17

Figure 2-17: RESET/LOCK Example

CLKIN

RST

CLK0

CLK90

CLK180

CLKFX

CLKFX180

CLKDV

LOCKED

1 2

3 Periods

LOCK

DLL

ug190_2_18_042406

Loading...

Loading...