142 www.xilinx.com Virtex-5 FPGA User Guide

UG190 (v5.0) June 19, 2009

Chapter 4: Block RAM

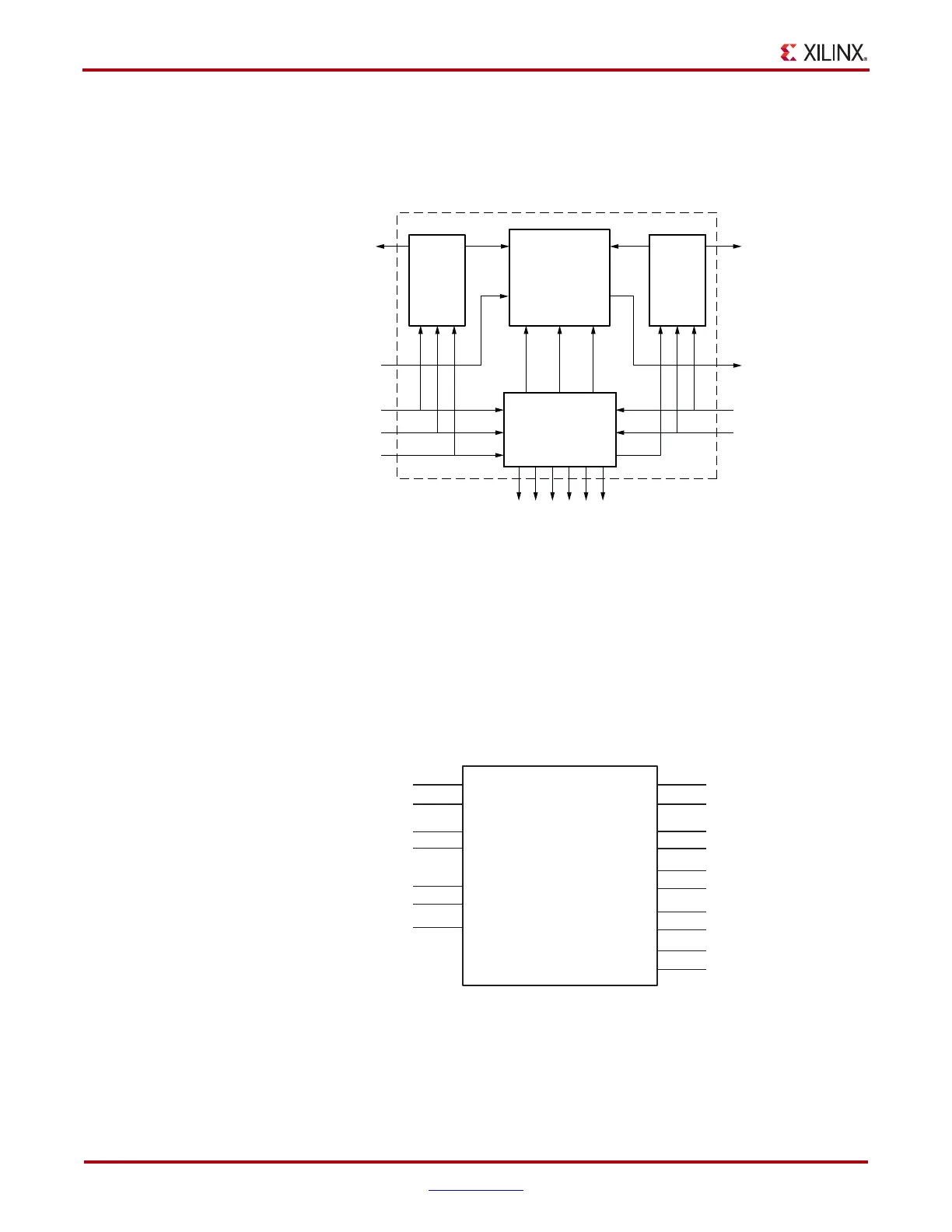

FIFO Architecture: a Top-Level View

Figure 4-17 shows a top-level view of the Virtex-5 FIFO architecture. The read pointer,

write pointer, and status flag logic are dedicated for FIFO use only.

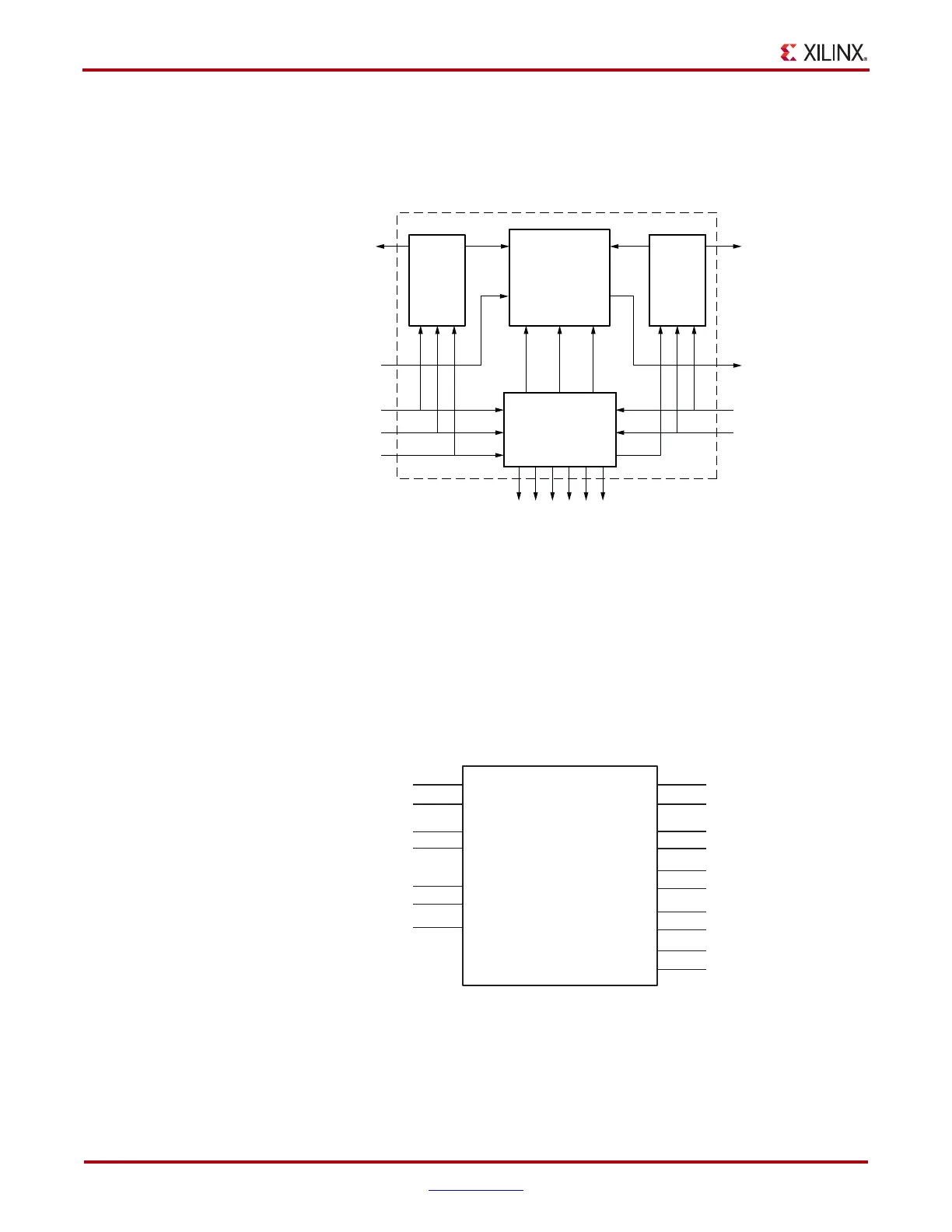

FIFO Primitives

Figure 4-18 shows the FIFO36 primitive.

X-Ref Target - Figure 4-17

Figure 4-17: Top-Level View of FIFO in Block RAM

Block

RAM

WRCOUNT RDCOUNT

WRCLK

WREN

RDCLK

DO/DOPDIN/DINP

RDEN

RST

Status Flag

Logic

FULL

EMPTY

ALMOSTFULL

ALMOSTEMPTY

RDERR

WRERR

waddr raddr

oe

mem_ren

mem_wen

Write

Pointer

Read

Pointer

ug190_4_27_061906

X-Ref Target - Figure 4-18

Figure 4-18: FIFO36 Primitive

DOP[3:0]

DI[31:0]

DIP[3:0]

RDEN

RST

RDCLK

WREN

WRCLK

DO[31:0]

RDCOUNT[12:0]

WRCOUNT[12:0]

EMPTY

FULL

ALMOSTEMPTY

ALMOSTFULL

WRERR

RDERR

FIFO36

ug190_4_15_021107

Loading...

Loading...