186 www.xilinx.com Virtex-5 FPGA User Guide

UG190 (v5.0) June 19, 2009

Chapter 5: Configurable Logic Blocks (CLBs)

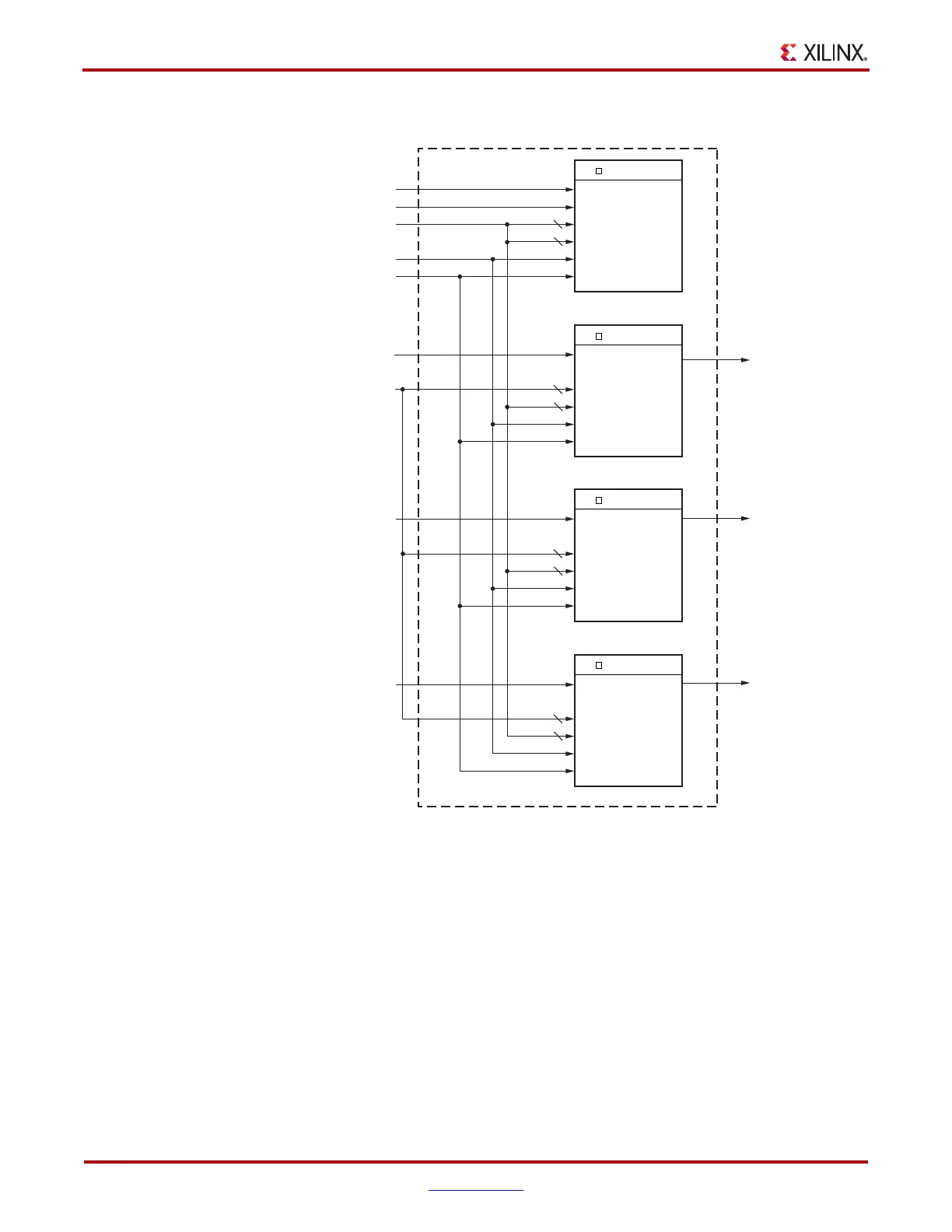

Implementation of distributed RAM configurations with depth greater than 64 requires the

usage of wide-function multiplexers (F7AMUX, F7BMUX, and F8MUX).

X-Ref Target - Figure 5-11

Figure 5-11: Distributed RAM (RAM64X3SDP)

UG190_5_06_050506

DI1

O[1]

O[2]

O[3]

DI2

unused

unused

WADDR[6:1]

RADDR[6:1]

DATA[1]

DATA[2]

DATA[3]

WCLK

WED

(CLK)

(WE)

6

6

DPRAM32

RAM 64X3SDP

A[6:1]

WA[6:1]

CLK

WE

DI1

DI2

6

6

DPRAM32

A[6:1]

WA[6:1]

CLK

WE

O6

DI1

DI2

DI2

B[6:1]

C[6:1]

D[6:1]

A[6:1]

6

6

DPRAM32

A[6:1]

WA[6:1]

CLK

WE

O6

DI1

6

6

DPRAM32

A[6:1]

WA[6:1]

CLK

WE

O6

O5

O5

O5

Loading...

Loading...