124 www.xilinx.com Virtex-5 FPGA User Guide

UG190 (v5.0) June 19, 2009

Chapter 4: Block RAM

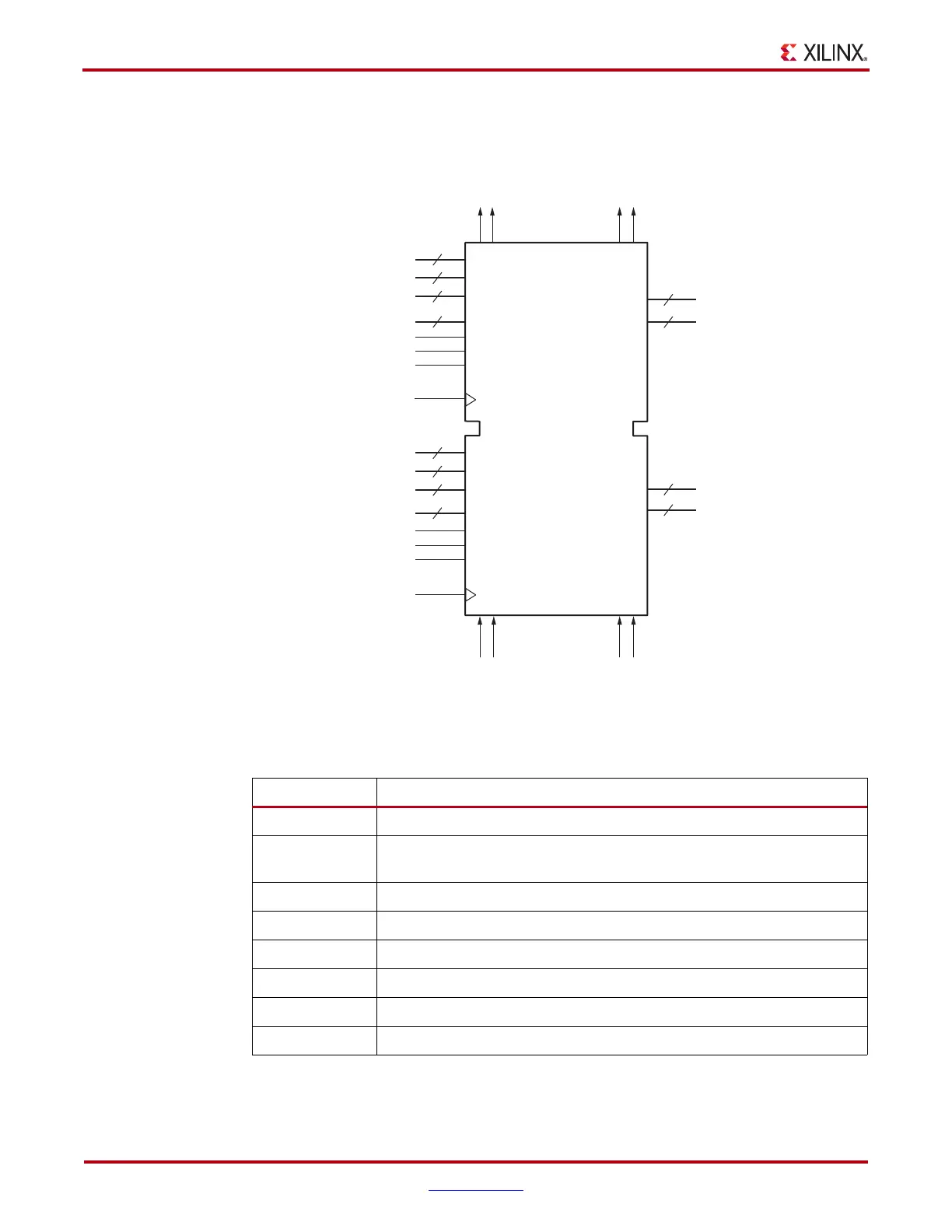

Figure 4-9 illustrates all the I/O ports of the 36 Kb true dual-port block RAM primitive

(RAMB36). Table 4-5 lists these primitives.

X-Ref Target - Figure 4-9

Figure 4-9: Block RAM Port Signals (RAMB36)

Table 4-5: Virtex-5 FPGA Block RAM, FIFO, Simple Dual Port, and ECC Primitives

Primitive Description

RAMB36 Supports port widths of x1, x2, x4, x9, x18, x36

RAMB36SDP Simple dual port (port width x72) and 64-bit ECC primitive (see

Figure 4-29)

FIFO36 Supports port widths of x4, x9, x18, x36

FIFO36_72 FIFO (port width x72), optional ECC support

RAMB18 Supports port widths of x1, x2, x4, x9, x18

RAMB18SDP Simple dual port (port width x36)

FIFO18 Supports port widths of x4, x9, x18

FIFO18_36 FIFO (port width x36)

Notes:

1. All eight primitives are described in the software Libraries guide as well as the language templates.

DOPA

DOPB

DIA

DIPA

ADDRA

WEA

ENA

SSRA

CLKA

DOA

DOB

REGCEA

DIB

DIPB

ADDRB

WEB

ENB

SSRB

REGCEB

CLKB

ug0190_4_10_100906

32

4

16

4

32

4

32

4

32

4

16

4

CASCADEOUTLATA CASCADEOUTLATB

CASCADEOUTREGA CASCADEOUTREGB

CASCADEINLATA CASCADEINLATB

CASCADEINREGA CASCADEINREGB

Loading...

Loading...