Virtex-5 FPGA User Guide www.xilinx.com 199

UG190 (v5.0) June 19, 2009

CLB Overview

carry multiplexer (MUXCY) can also be used to cascade function generators for

implementing wide logic functions.

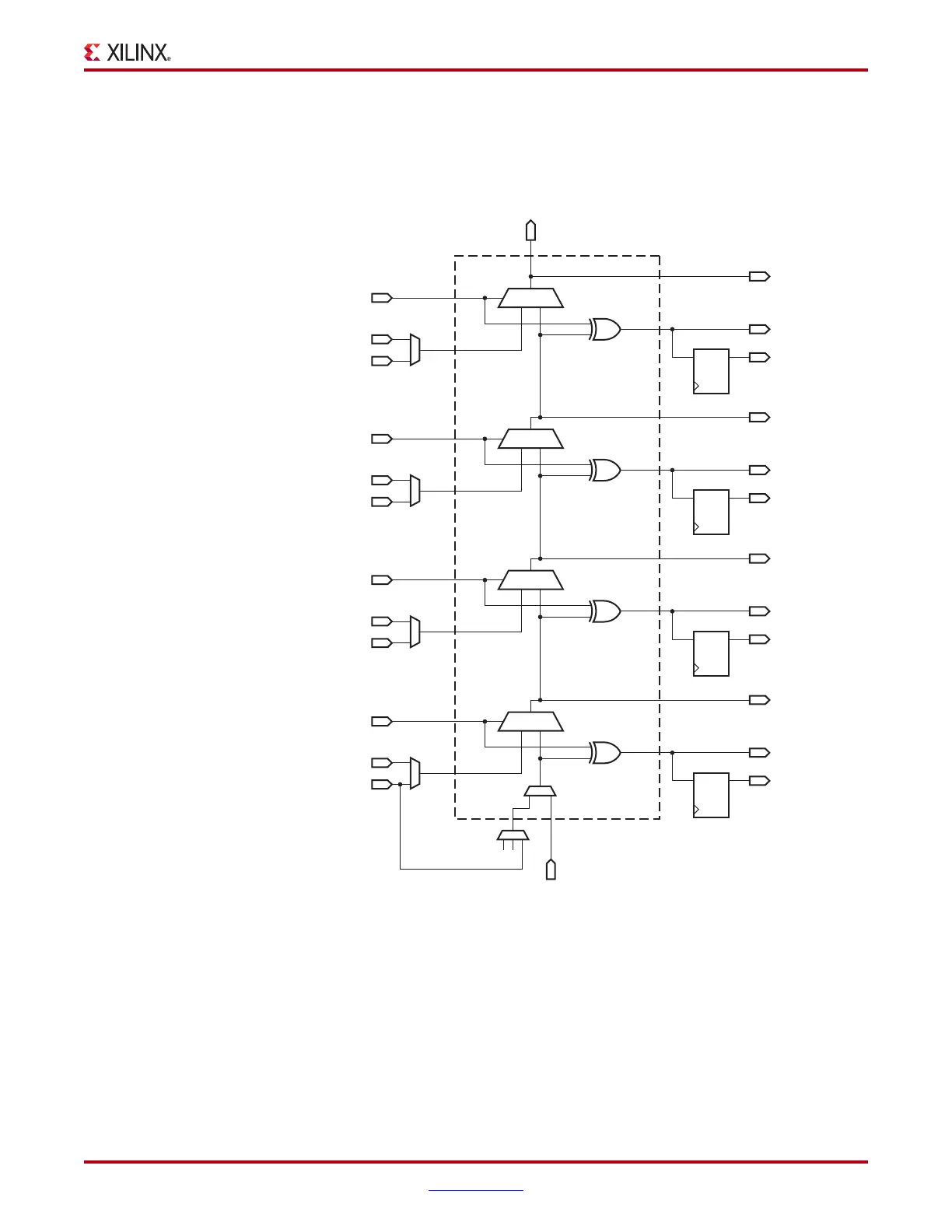

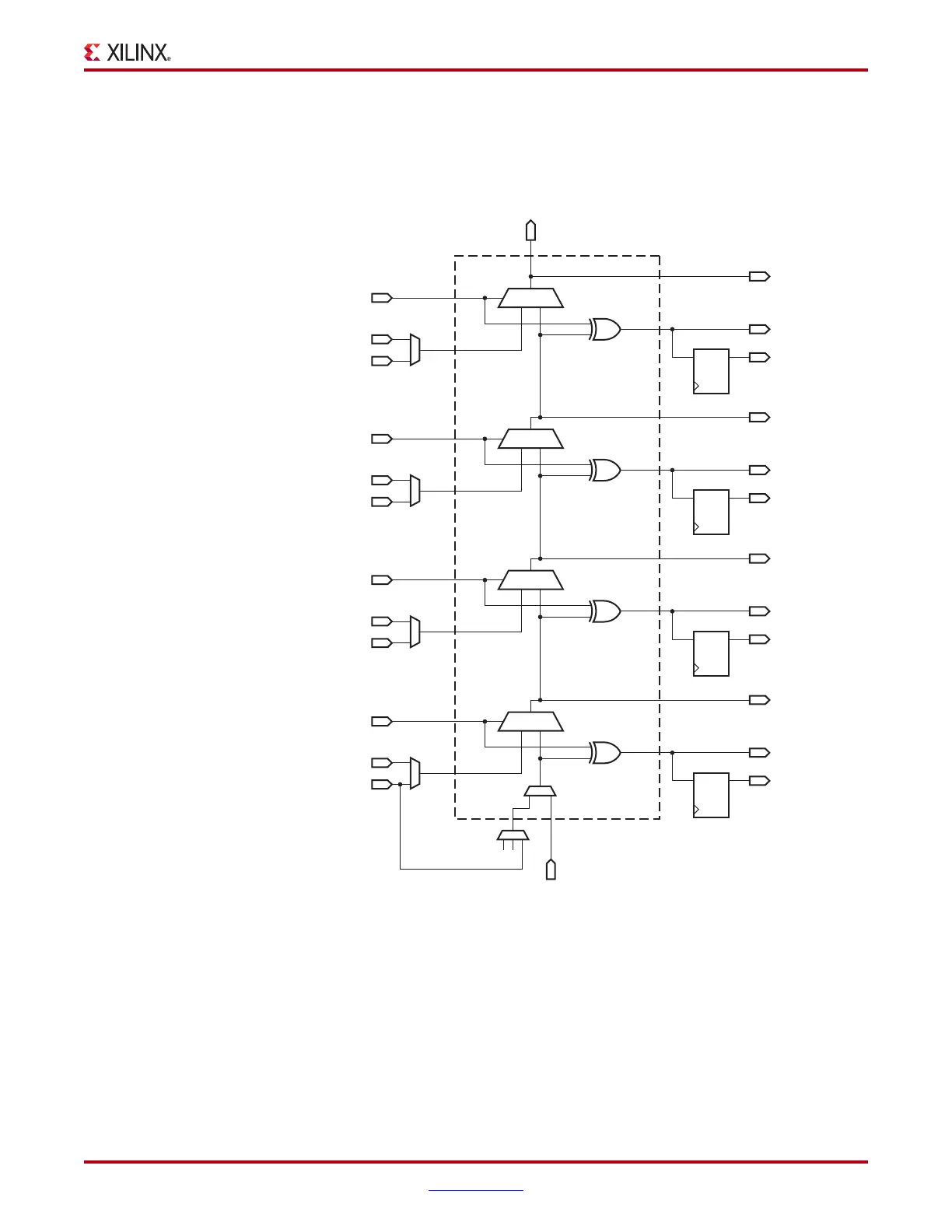

Figure 5-24 illustrates the carry chain with associated logic elements in a slice.

The carry chains carry lookahead logic along with the function generators. There are ten

independent inputs (S inputs – S0 to S3, DI inputs – DI1 to DI4, CYINIT and CIN) and eight

independent outputs (O outputs – O0 to O3, and CO outputs – CO0 to CO3).

The S inputs are used for the “propagate” signals of the carry lookahead logic. The

“propagate” signals are sourced from the O6 output of a function generator. The DI inputs

are used for the “generate” signals of the carry lookahead logic. The “generate” signals are

sourced from either the O5 output of a function generator or the BYPASS input (AX, BX,

CX, or DX) of a slice. The former input is used to create a multiplier, while the latter is used

X-Ref Target - Figure 5-24

Figure 5-24: Fast Carry Logic Path and Associated Elements

UG190_5_24_050506

O6 From LUTD

DMUX/DQ*

DMUX

DQ

O5 From LUTD

DX

S3

MUXCY

DI3

CO3

O3

COUT (To Next Slice)

Carry Chain Block

(CARRY4)

(Optional)

DQ

O6 From LUTC

CMUX/CQ*

CMUX

CQ

O5 From LUTC

CX

S2

MUXCY

DI2

CO2

CO1

CO0

O2

(Optional)

DQ

O6 From LUTB

BMUX/BQ*

BMUX

BQ

O5 From LUTB

BX

S1

MUXCY

DI1

O1

(Optional)

DQ

O6 From LUTA

AMUX/AQ*

AMUX

AQ

O5 From LUTA

AX

S0

MUXCY

DI0

CIN

CIN (From Previous Slice)

* Can be used if

unregistered/registered

outputs are free.

CYINIT

10

O0

(Optional)

DQ

Loading...

Loading...