Virtex-5 FPGA User Guide www.xilinx.com 179

UG190 (v5.0) June 19, 2009

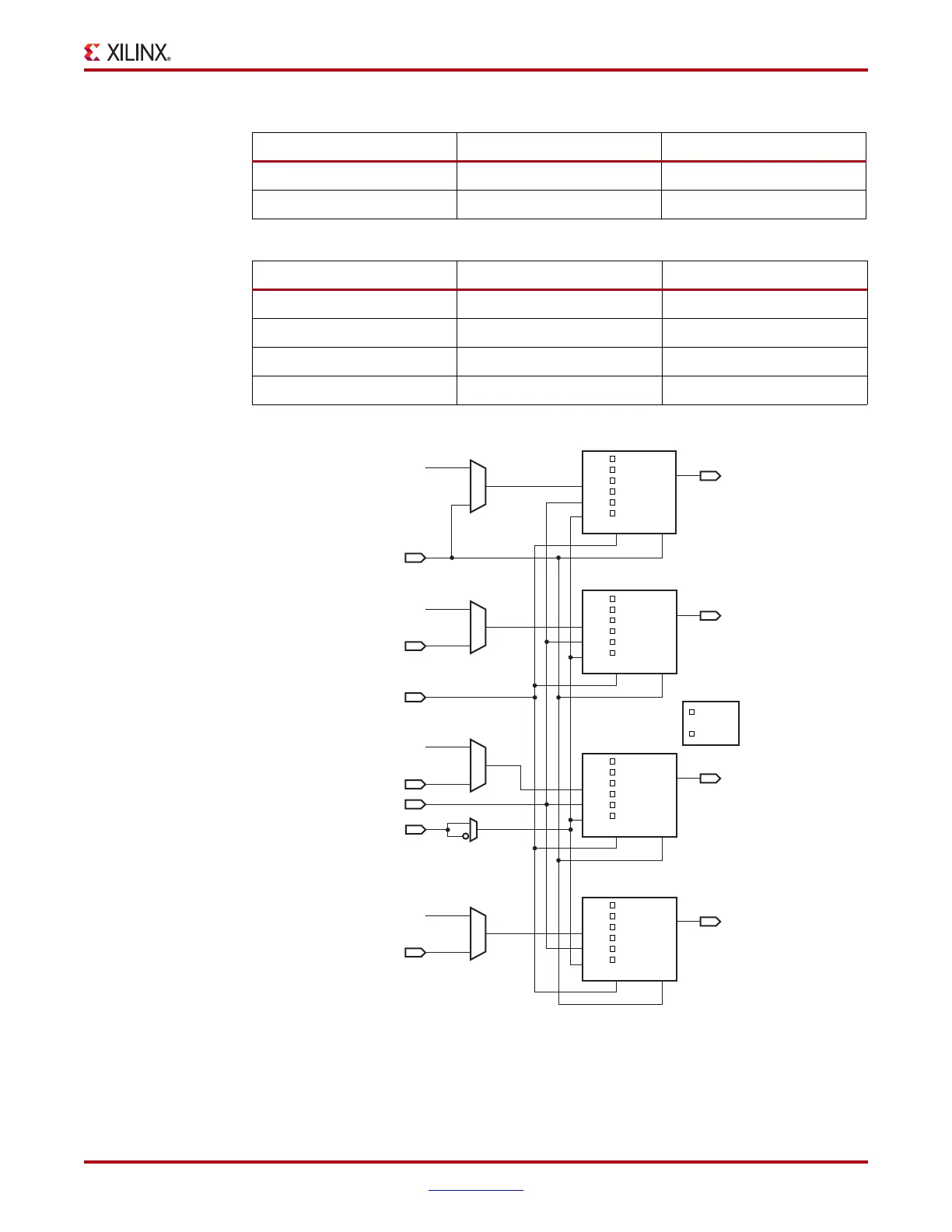

CLB Overview

SRHIGH and SRLOW can be set individually for each storage element in a slice. The choice

of synchronous (SYNC) or asynchronous (ASYNC) set/reset (SRTYPE) cannot be set

individually for each storage element in a slice.

100

110

Table 5-4: Truth Table when SRHIGH is Used

SR REV Function

0 0 No Logic Change

010

101

110

X-Ref Target - Figure 5-5

Figure 5-5: Register/Latch Configuration in a Slice

Table 5-3: Truth Table when SRLOW is Used (Default Condition) (Continued)

SR REV Function

UG190_5_05_071207

DX

CX

BX

CE

AX

DQ

CQ

BQ

AQ

D

FF

LATCH

INIT1

INIT0

SRHIGH

SRLOW

SR REV

DFF

LUT D Output

LUT C Output

CE

CK

D

FF

LATCH

INIT1

INIT0

SRHIGH

SRLOW

SR REV

CE

CK

D

FF

LATCH

INIT1

INIT0

SRHIGH

SRLOW

SR REV

CE

CK

D

FF

LATCH

INIT1

INIT0

SRHIGH

SRLOW

SR REV

Q

CE

CK

Q

Q

Q

SR

LUT B Output

LUT A Output

AFF

BFF

CFF

CLK

Reset Type

Sync

Async

Loading...

Loading...