78 www.xilinx.com Virtex-5 FPGA User Guide

UG190 (v5.0) June 19, 2009

Chapter 2: Clock Management Technology

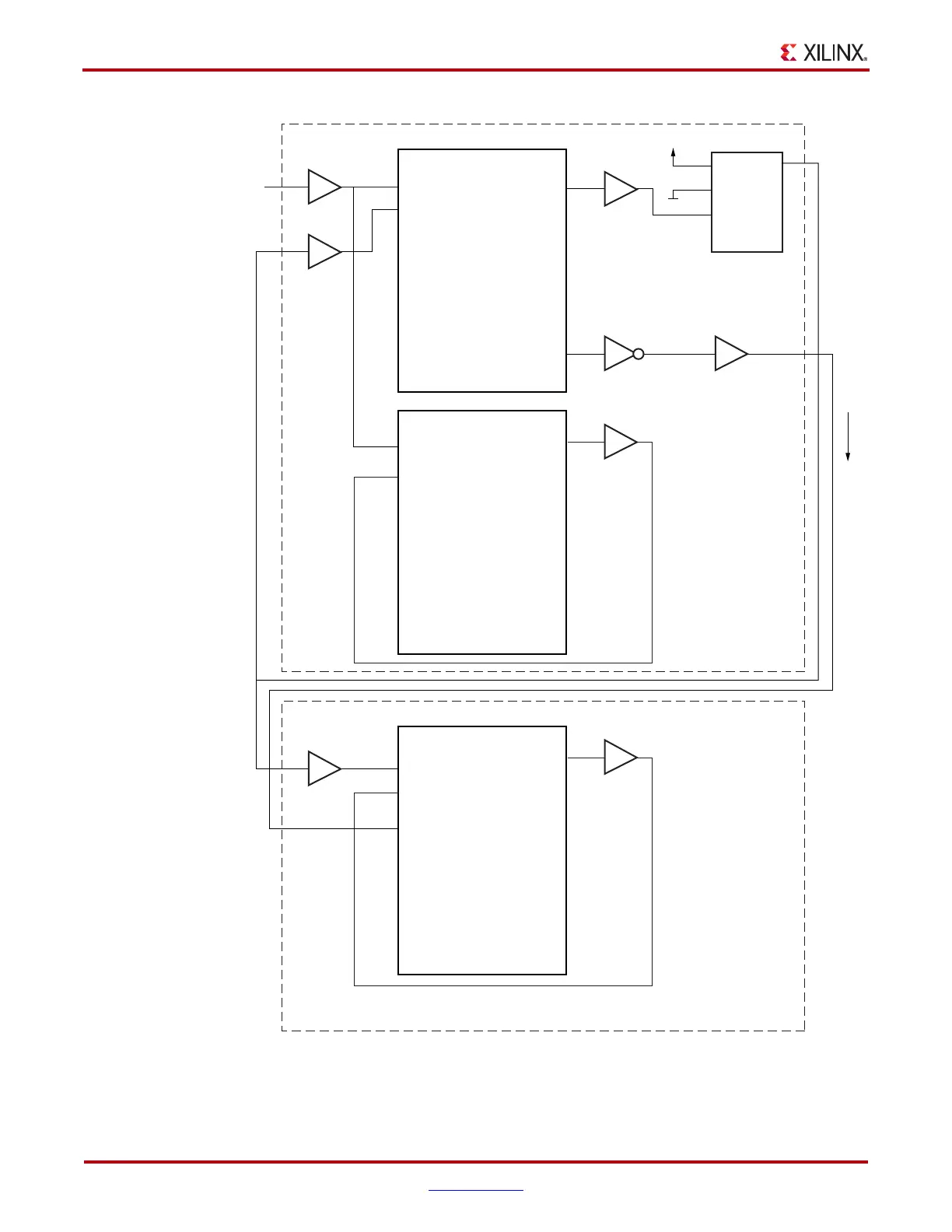

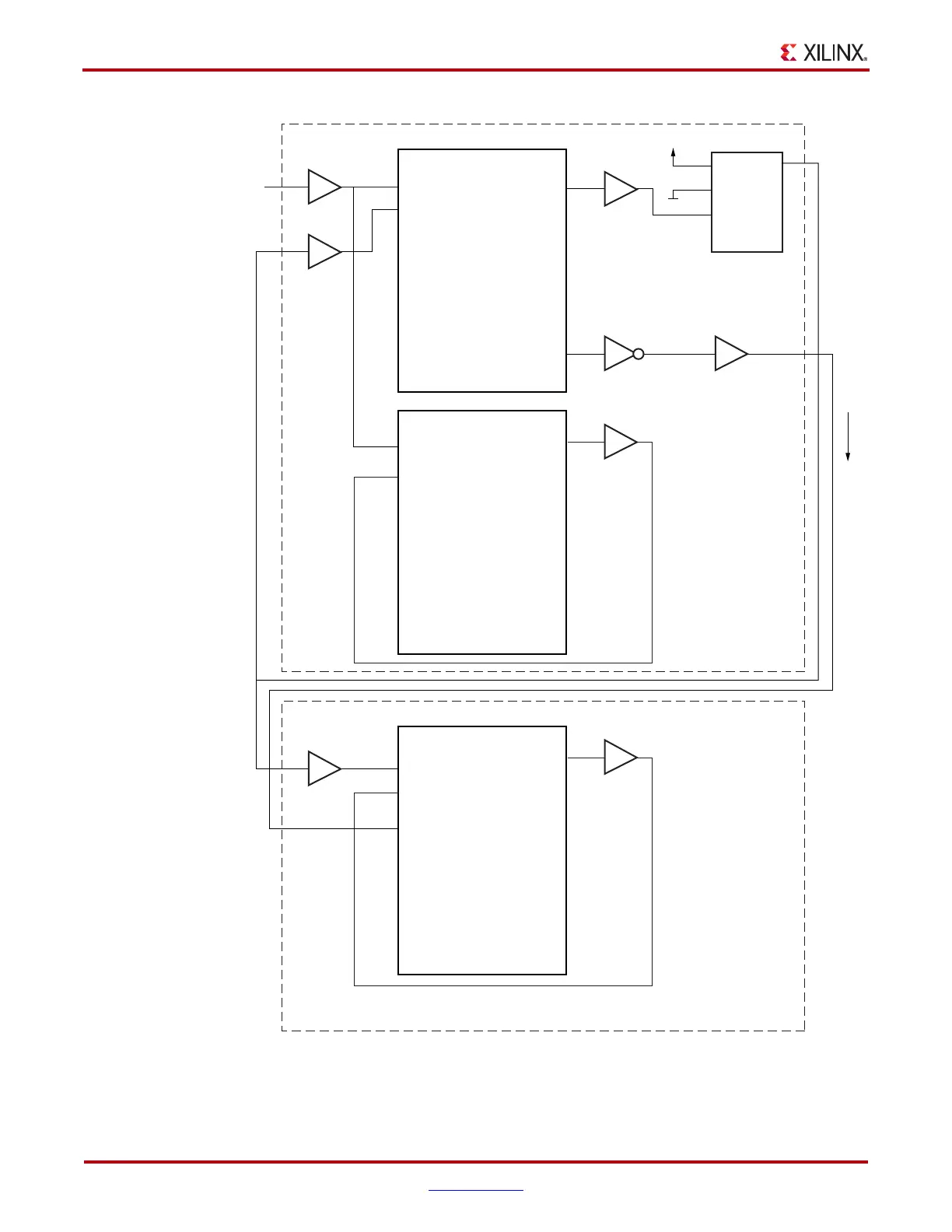

X-Ref Target - Figure 2-11

Figure 2-11: Board Deskew with Internal Deskew Interfacing to Other Virtex

Devices

CLKIN

CLK0

CLK90

CLK180

CLK270

CLK2X

CLK2X180

CLKDV

CLKFX

CLKFX180

LOCKED

DO(15:0)

CLKFB

RST

PSINCDEC

PSEN

PSCLK

DADDR[6:0]

DI[15:0]

DWE

DEN

DCLK

CLKIN

CLK0

CLK90

CLK180

CLK270

CLK2X

CLK2X180

CLKDV

CLKFX

CLKFX180

LOCKED

DO[15:0]

CLKFB

RST

PSINCDEC

PSEN

PSCLK

DADDR[6:0]

DI[15:0]

DWE

DEN

DCLK

IBUFG

DCM_ADV

DCM_ADV

IBUFG

IBUFG

BUFG

GND

BUFG

INV OBUF

BUFG

ug190_2_12_032506

D1

D2

C

Q

ODDR

Virtex-5 FPGA

CLKIN

CLK0

CLK90

CLK180

CLK270

CLK2X

CLK2X180

CLKDV

CLKFX

CLKFX180

LOCKED

DO[15:0]

CLKFB

RST

PSINCDEC

PSEN

PSCLK

DADDR[6:0]

DI[15:0]

DWE

DEN

DCLK

DCM_ADV

Virtex-5 FPGA

This circuit can be duplicated to multiple Virtex devices. Use CLKDLL

for Virtex and Virtex-E devices, DCM for Virtex-II and Virtex-II Pro devices.

V

CC

to

RST

Loading...

Loading...