Virtex-5 FPGA User Guide www.xilinx.com 99

UG190 (v5.0) June 19, 2009

General Usage Description

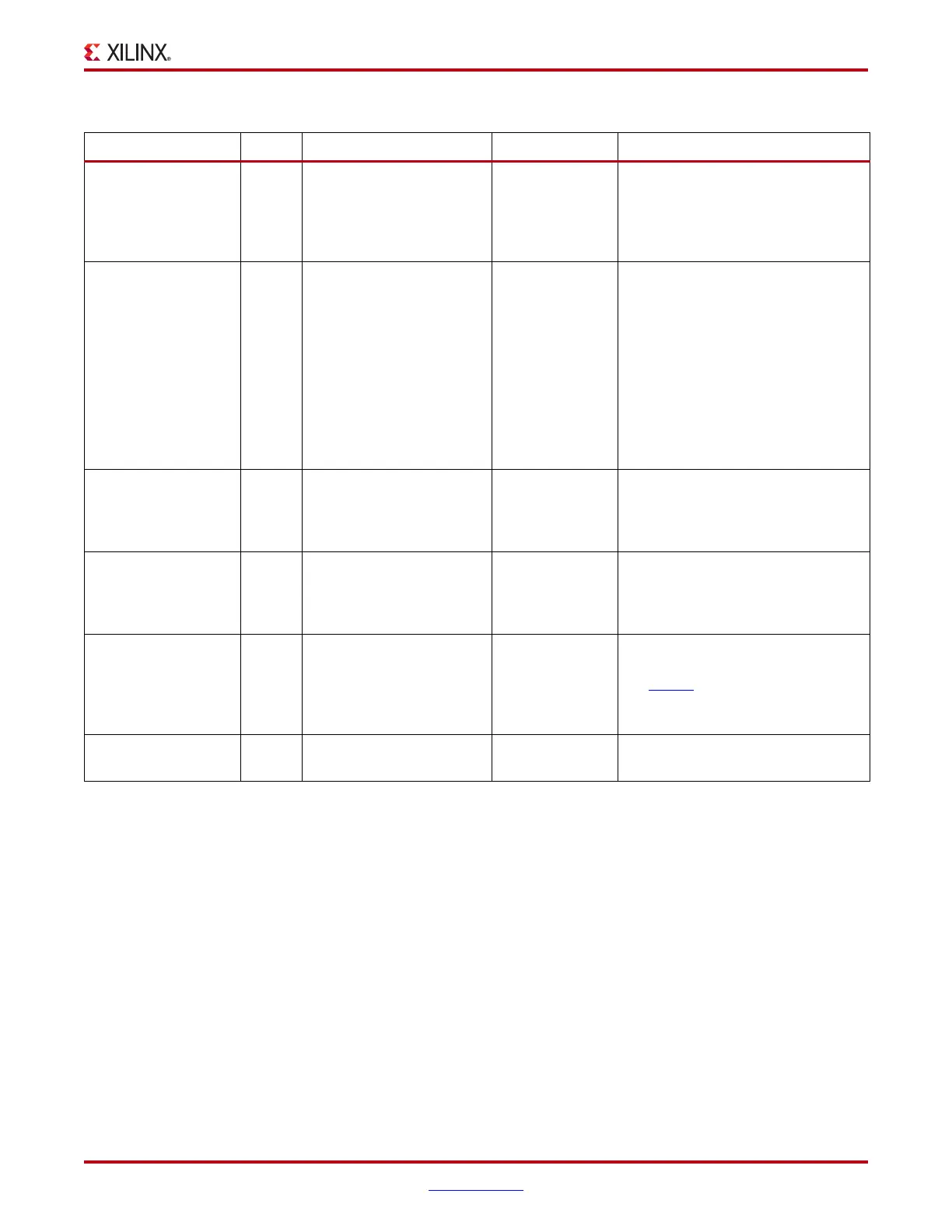

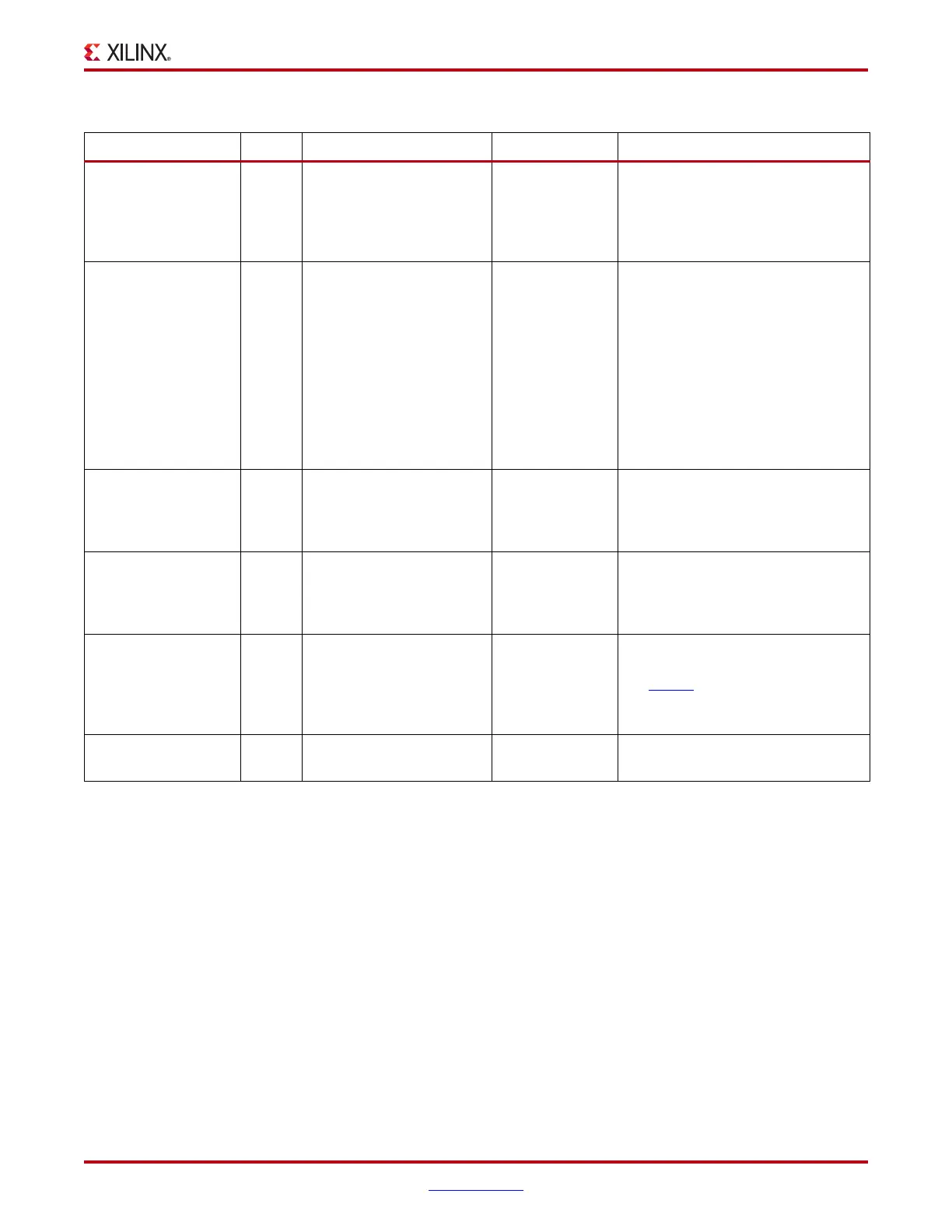

CLKFBOUT_PHASE Real 0.0 to 360.0 0.0 Specifies the phase offset in degrees

of the clock feedback output. Shifting

the feedback clock results in a

negative phase shift of all output

clocks to the PLL.

REF_JITTER Real 0.000 to 0.999 0.100 Allows specification of the expected

jitter on the reference clock in order to

better optimize PLL performance. A

bandwidth setting of OPTIMIZED

will attempt to choose the best

parameter for input clocking when

unknown. If known, then the value

provided should be specified in

terms of the UI percentage (the

maximum peak to peak value) of the

expected jitter on the input clock.

CLKIN1_PERIOD Real 1.408 to 52.630 0.000 Specifies the input period in ns to the

PLL CLKIN1 input. Resolution is

down to the ps. This information is

mandatory and must be supplied.

CLKIN2_PERIOD Real 1.408 to 52.630 0.000 Specifies the input period in ns to the

PLL CLKIN2 input. Resolution is

down to the ps. This information is

mandatory and must be supplied.

CLKOUT[0:5]_

DESKEW_ADJUST

String PPC or None None Fixed delay used when the PLL is

used in a PPC440 system.

See UG200

: Embedded Processor Block

in Virtex-5 FPGAs Reference Guide for

details.

RESET_ON_LOSS

_OF_LOCK

String FALSE FALSE Must be set to FALSE, not supported

in silicon.

Table 3-4: PLL Attributes (Continued)

Attribute Type Allowed Values Default Description

Loading...

Loading...