112 www.xilinx.com Virtex-5 FPGA User Guide

UG190 (v5.0) June 19, 2009

Chapter 3: Phase-Locked Loops (PLLs)

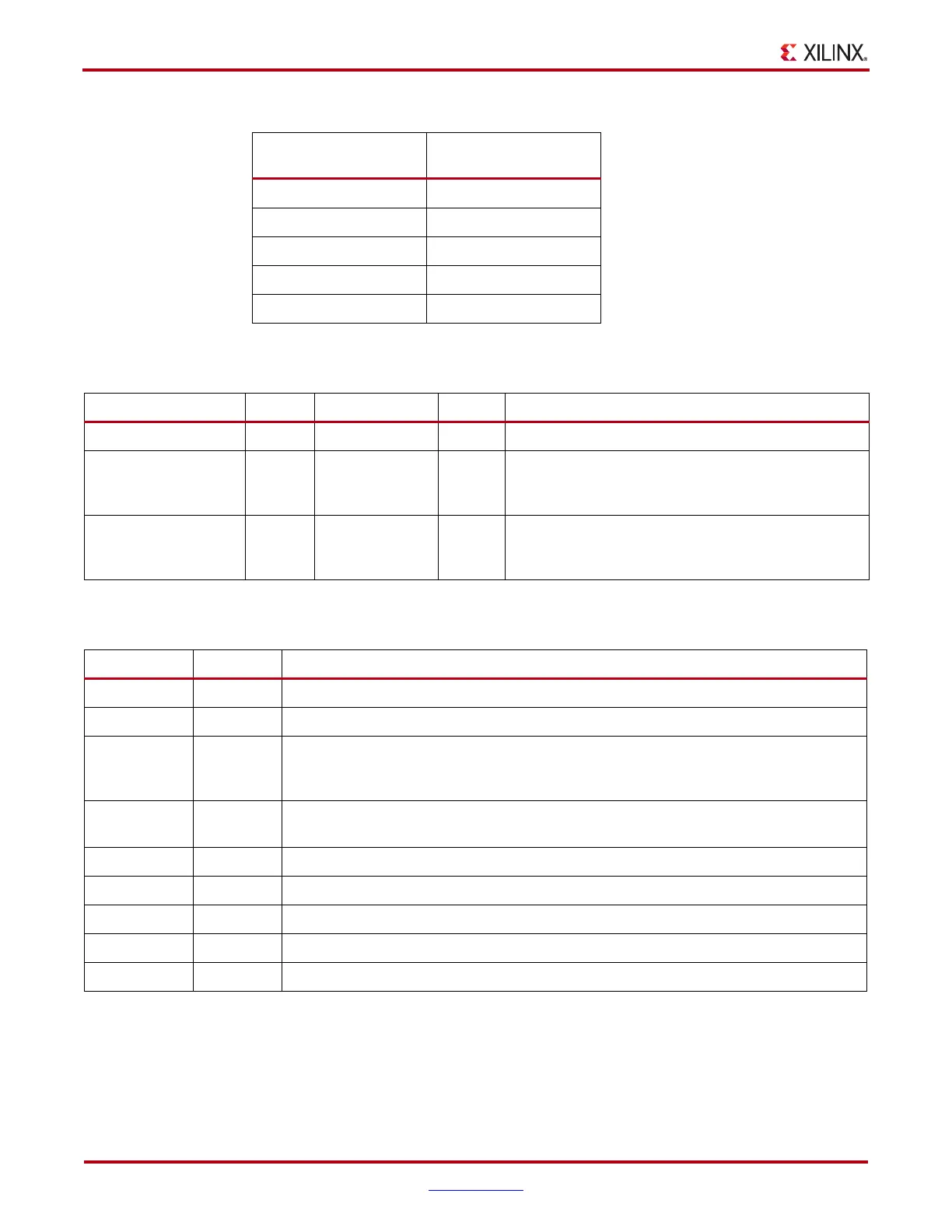

Table 3-9 shows the PLL attributes in Virtex-4 FPGA PMCD legacy mode.

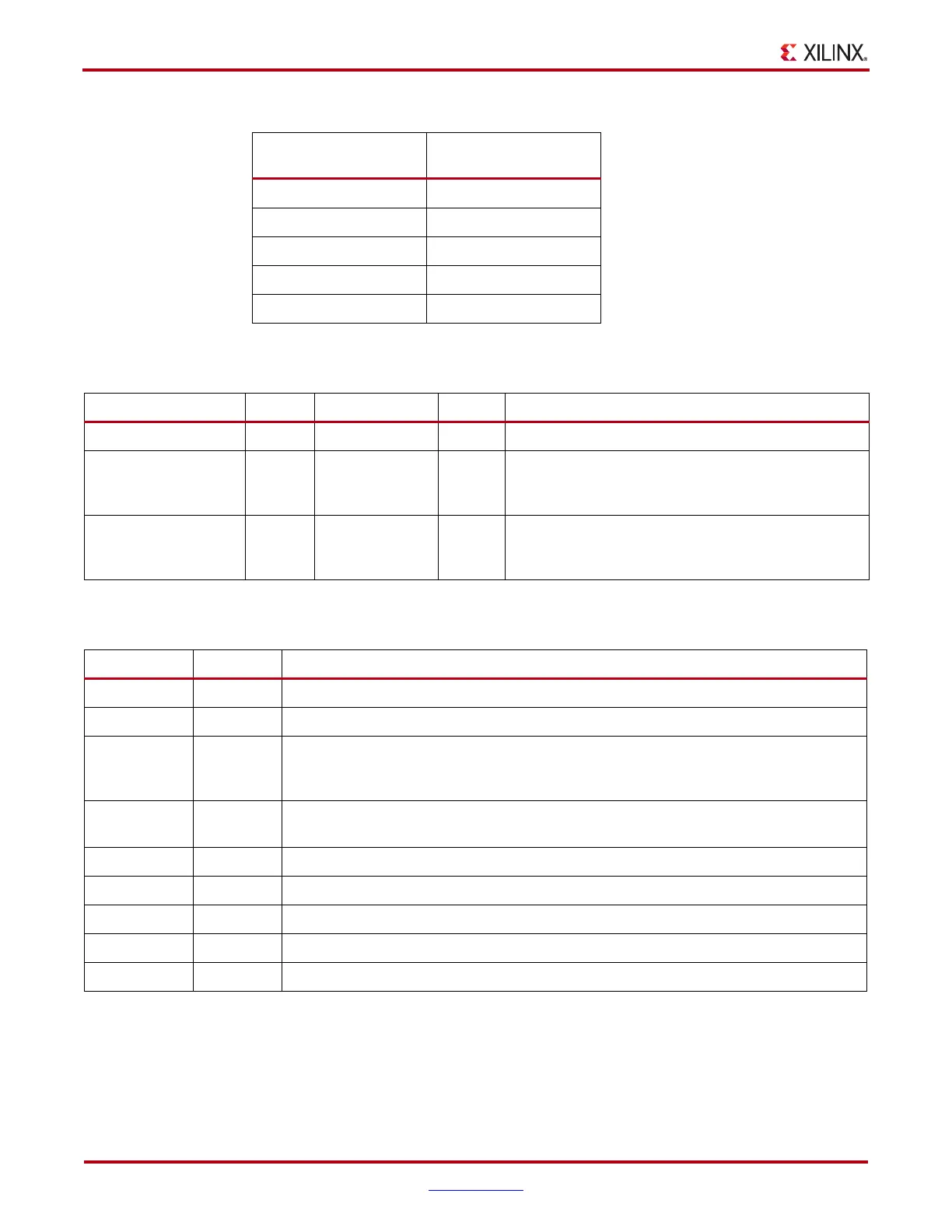

Table 3-10 shows the PLL ports in Virtex-4 FPGA PMCD legacy mode.

CLKB1 CLKFBOUT

CLKC1 n/a

CLKD1 n/a

RST RST

REL REL

Table 3-8: Mapping of Port Names (Continued)

Virtex-4 FPGA

Port Name

Virtex-5 FPGA

Port Name

Table 3-9: PLL Attributes When in Virtex-4 FPGA PMCD Legacy Mode

Attribute Type Allowed Values Default Description

PLL_PMCD_MODE Boolean TRUE or FALSE FALSE Enables PLL to act as PMCDs

EN_REL Boolean TRUE or FALSE FALSE

When in PMCD mode (PLL_PMCD_MODE = TRUE),

specifies release of divided clock CLKA outputs when

the REL input pin is asserted.

RST_DEASSERT_CLK String

CLKA

CLKB

CLKA

When in PMCD mode (PLL_PMCD_MODE = TRUE),

specifies a clock to synchronize with the release of

RST.

Table 3-10: PLL Ports in Virtex-4 FPGA PMCD Legacy Mode

Port Name I/O Pin Description

CLKFB Input Virtex-4 FPGA PMCD legacy mode CLKB input clock to the PMCD.

CLKIN Input Virtex-4 FPGA PMCD legacy mode CLKA input clock to the PMCD.

RST Input

RST is the reset input to the Virtex-4 FPGA PMCD legacy mode. Asserting RST signal

asynchronously forces all outputs Low. Deasserting RST synchronously allows all

outputs to toggle.

REL Input

REL is the release input to the Virtex-4 FPGA PMCD legacy mode. Asserting the REL

signal releases the divided outputs synchronous to CLKA.

CLKOUT0 Output Virtex-4 FPGA PMCD legacy mode CLKB1.

CLKOUT1 Output Virtex-4 FPGA PMCD legacy mode CLKA1.

CLKOUT2 Output Virtex-4 FPGA PMCD legacy mode CLKA1D2.

CLKOUT3 Output Virtex-4 FPGA PMCD legacy mode CLKA1D4.

CLKOUT4 Output Virtex-4 FPGA PMCD legacy mode CLKA1D8.

Loading...

Loading...