Virtex-5 FPGA User Guide www.xilinx.com 189

UG190 (v5.0) June 19, 2009

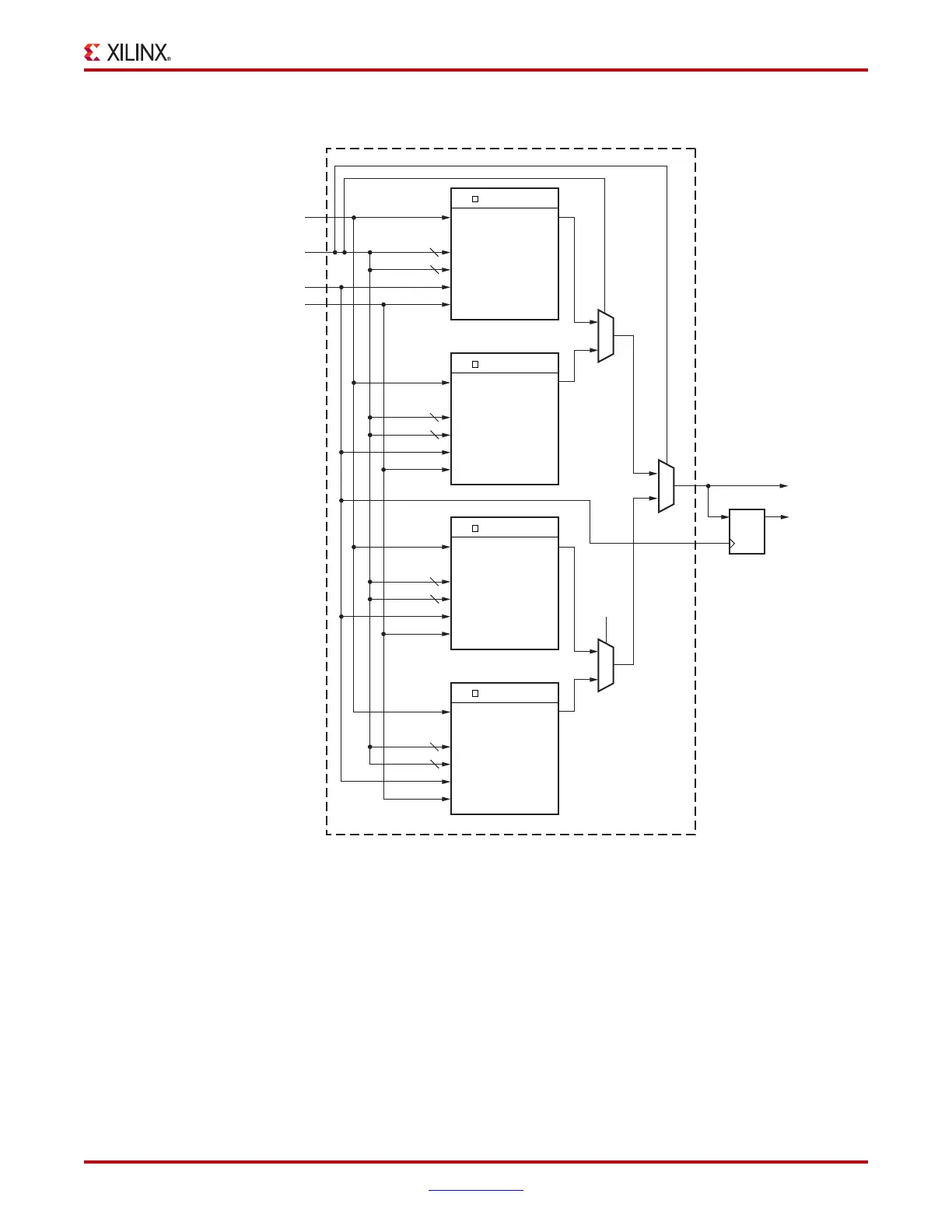

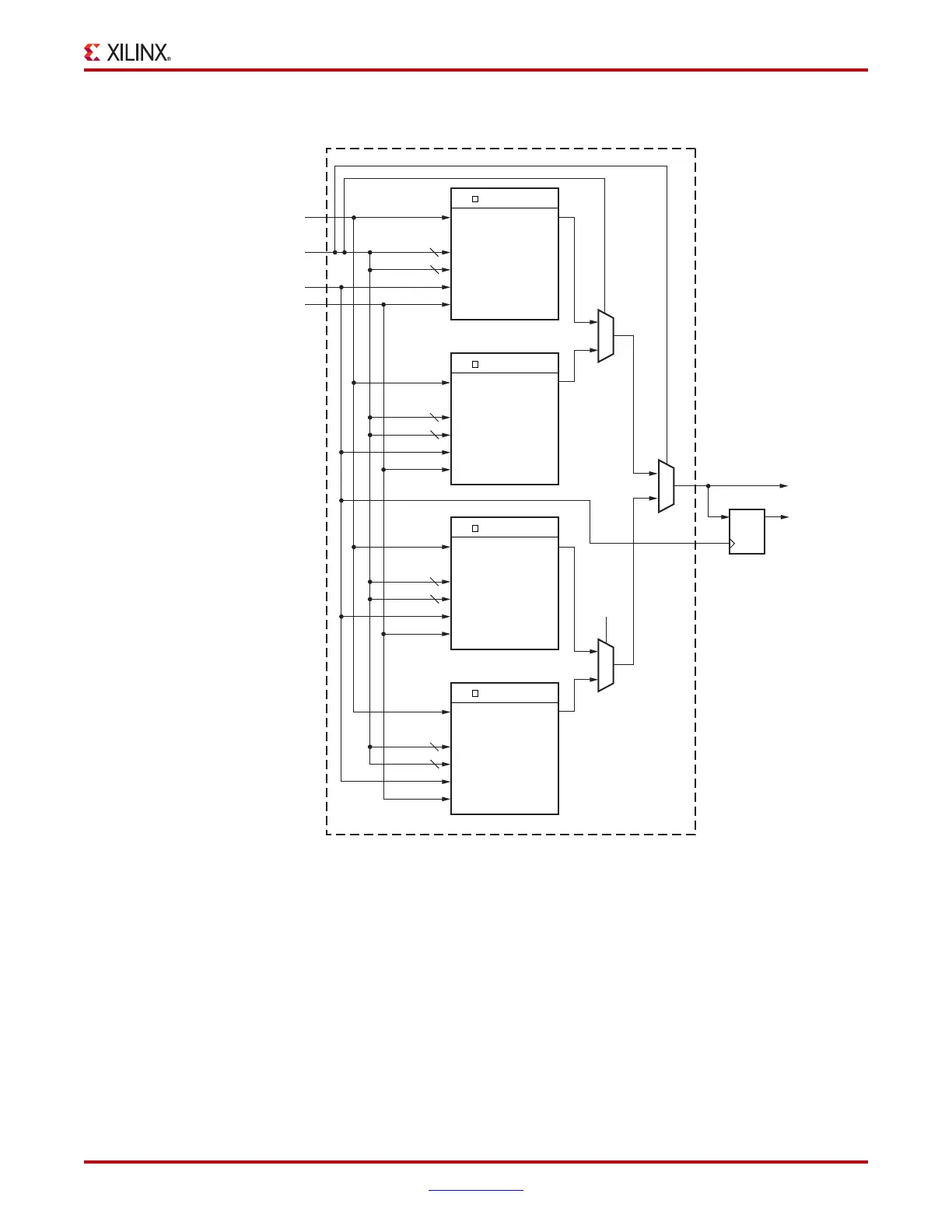

CLB Overview

Distributed RAM configurations greater than the provided examples require more than

one SLICEM. There are no direct connections between slices to form larger distributed

RAM configurations within a CLB or between slices.

X-Ref Target - Figure 5-14

Figure 5-14: Distributed RAM (RAM256X1S)

UG190_5_14_050506

DI1

D

A[7:0]

WCLK

WE

(CLK)

(WE/CE)

6

8

SPRAM64

RAM256X1S

A[6:1]

WA[8:1]

CLK

WE

O6

DI1

6

8

SPRAM64

A[6:1]

WA[8:1]

CLK

WE

O6

F7BMUX

F8MUX

Registered

Output

Output

(Optional)

DQ

O

DI1

6

8

SPRAM64

A[6:1]

WA[8:1]

CLK

WE

O6

DI1

6

8

SPRAM64

A[6:1]

WA[8:1]

CLK

WE

O6

F7AMUX

A6 (CX)

A6 (AX)

A7 (BX)

Loading...

Loading...