228 www.xilinx.com Virtex-5 FPGA User Guide

UG190 (v5.0) June 19, 2009

Chapter 6: SelectIO Resources

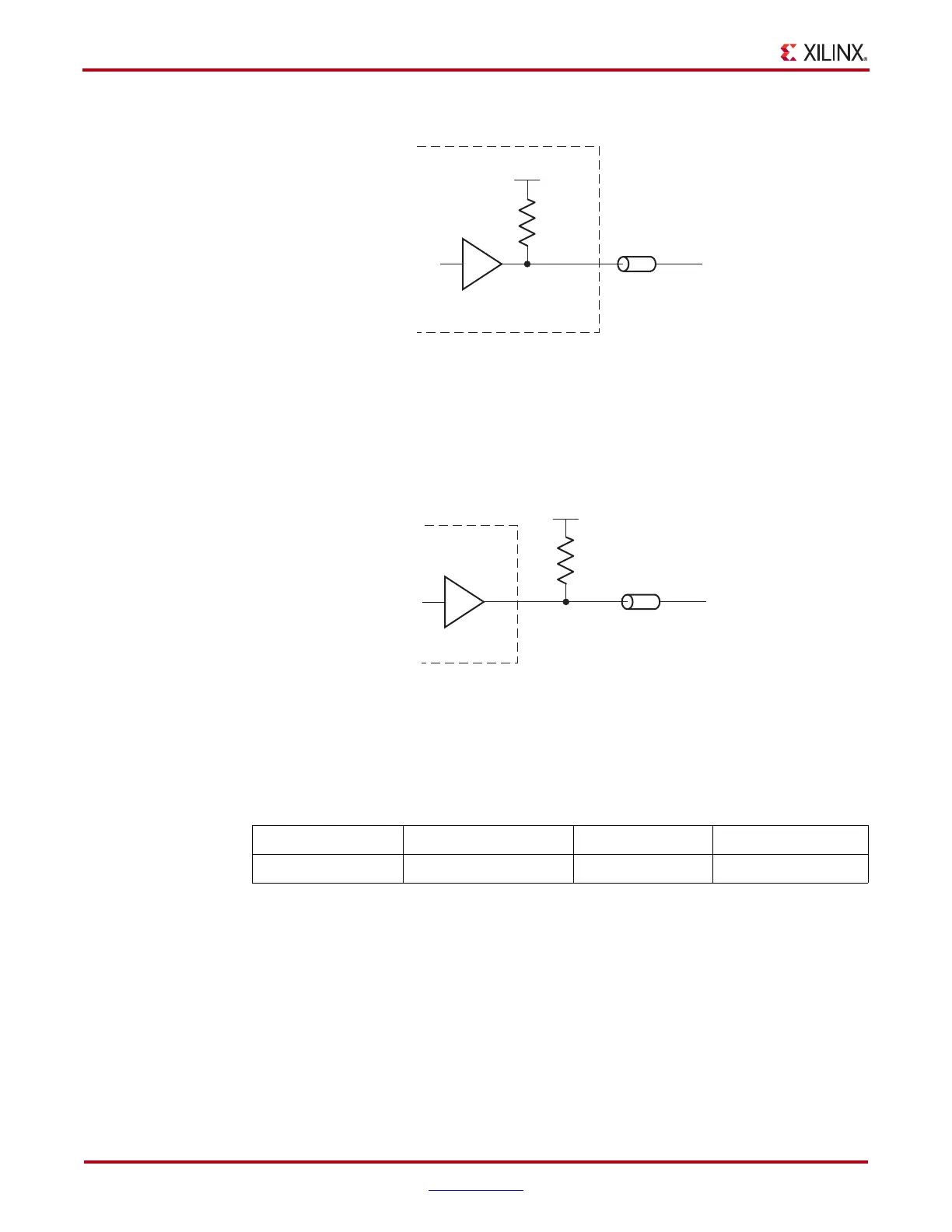

Figure 6-13 illustrates a driver with single termination inside a Virtex-5 device.

Driver with Termination to V

CCO

/2 (Split Termination)

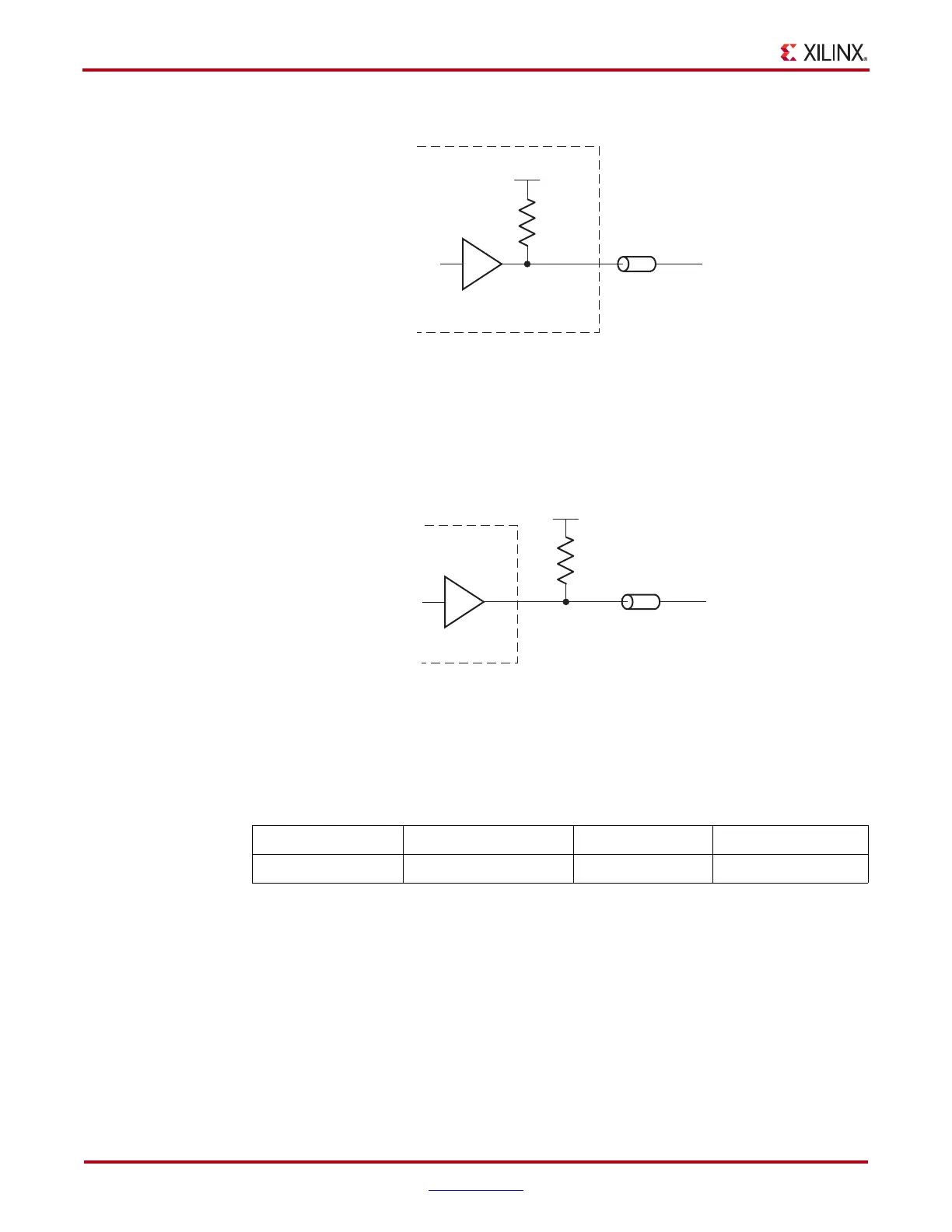

Some I/O standards, such as HSTL Class II, require an output termination to V

CCO

/2 (see

Figure 6-14).

DCI can provide output termination to V

CCO

/2 using split termination. DCI only controls

the impedance of the termination, but not the driver. Both HSTL and SSTL standards need

50 Ω external reference resistors. The DCI output standards supporting drivers with split

termination are shown in Table 6-2.

X-Ref Target - Figure 6-13

Figure 6-13: Driver with Termination to V

CCO

Using DCI Single Termination

R

UG190_6_11_021206

V

CCO

IOB

Z

0

Virtex-5 DCI

X-Ref Target - Figure 6-14

Figure 6-14: Driver with Termination to V

CCO

/2 without DCI

Table 6-2: DCI Output Standards Supporting Split Termination

HSTL_II_DCI DIFF_HSTL_II_DCI SSTL2_II_DCI DIFF_SSTL2_II_DCI

HSTL_II_DCI_18 DIFF_HSTL_II_DCI_18 SSTL18_II_DCI DIFF_SSTL18_II_DCI

R

UG190_c6_12_022609

V

CCO

/2

IOB

Z

0

Virtex-5 FPGA

Loading...

Loading...