266 www.xilinx.com Virtex-5 FPGA User Guide

UG190 (v5.0) June 19, 2009

Chapter 6: SelectIO Resources

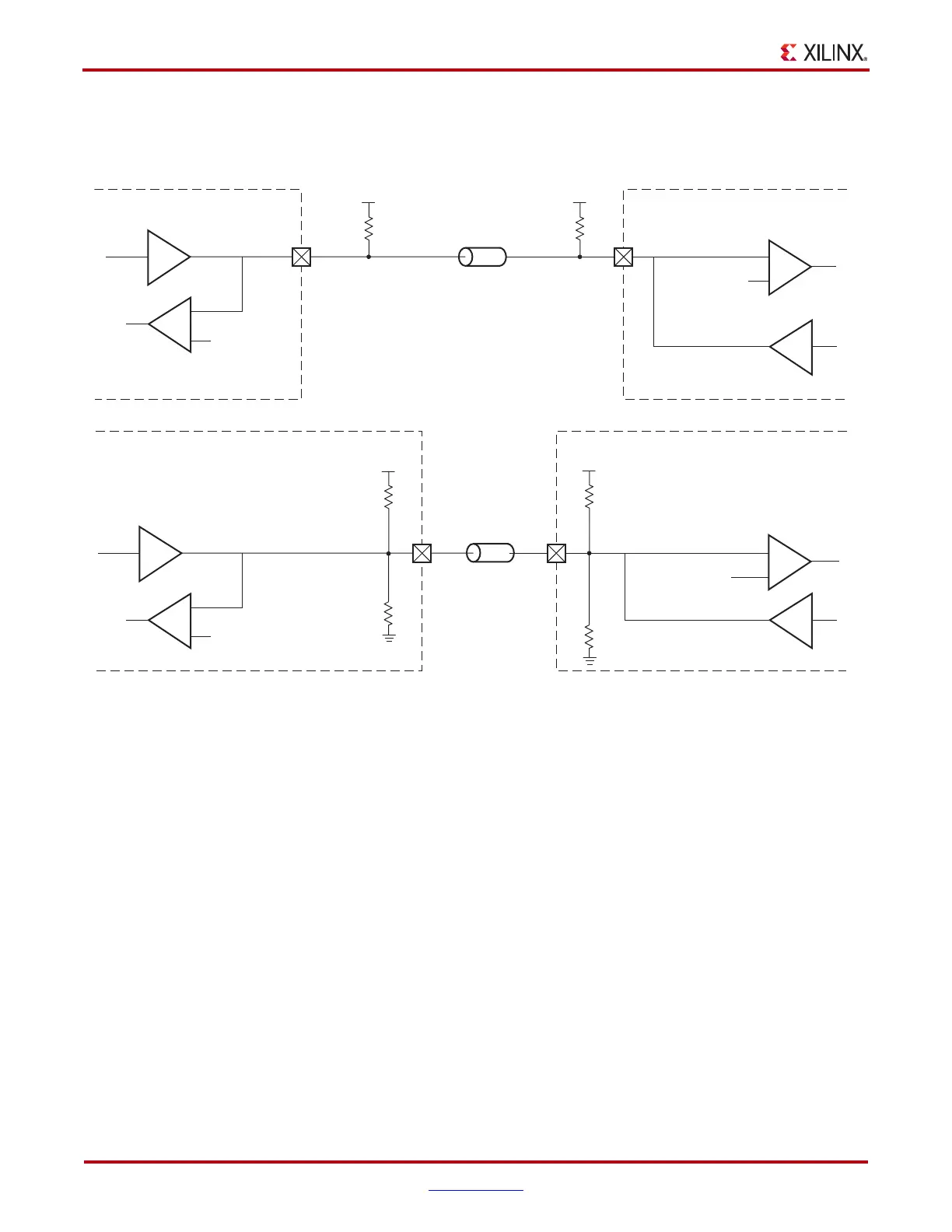

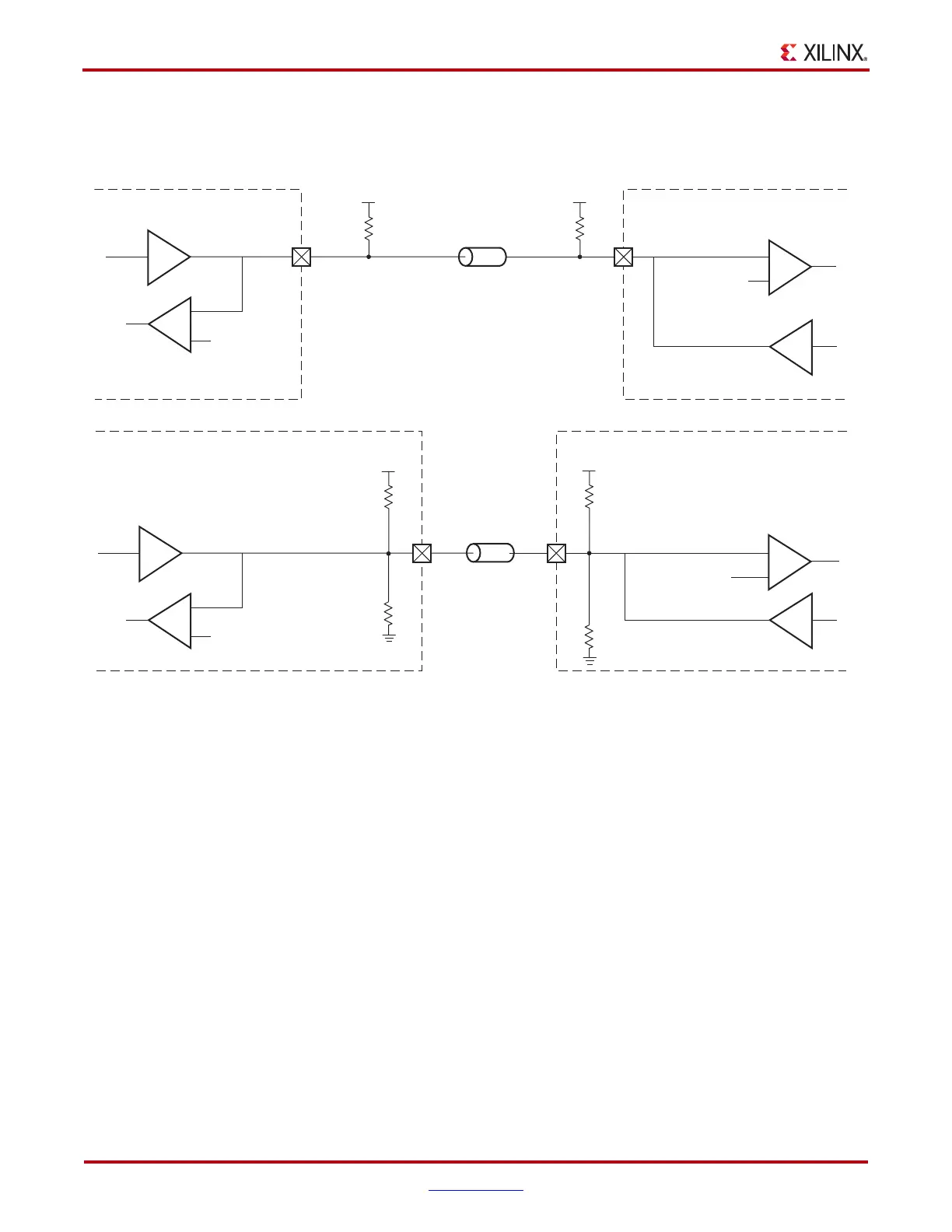

Figure 6-57 shows a sample circuit illustrating a valid termination technique for HSTL

Class II (1.8V) with bidirectional termination.

X-Ref Target - Figure 6-57

Figure 6-57: HSTL Class II (1.8V) with Bidirectional Termination

Z

0

IOB

IOB

HSTL_II_18

HSTL_II_18

ug190_6_54_030306

V

TT

= 0.9V

R

P

= Z

0

= 50Ω

V

TT

= 0.9V

R

P

= Z

0

= 50Ω

Z

0

IOB

IOB

HSTL_II_DCI_18

HSTL_II_DCI_18

V

CCO

= 1.8V

2R

VRP

= 2Z

0

= 100Ω

2R

VRN

= 2Z

0

= 100Ω

V

REF

= 0.9V

V

REF

= 0.9V

+

–

V

REF

= 0.9V

+

–

External Termination

DCI

V

CCO

= 1.8V

2R

VRP

= 2Z

0

= 100Ω

2R

VRN

= 2Z

0

= 100Ω

V

REF

= 0.9V

Loading...

Loading...