308 www.xilinx.com Virtex-5 FPGA User Guide

UG190 (v5.0) June 19, 2009

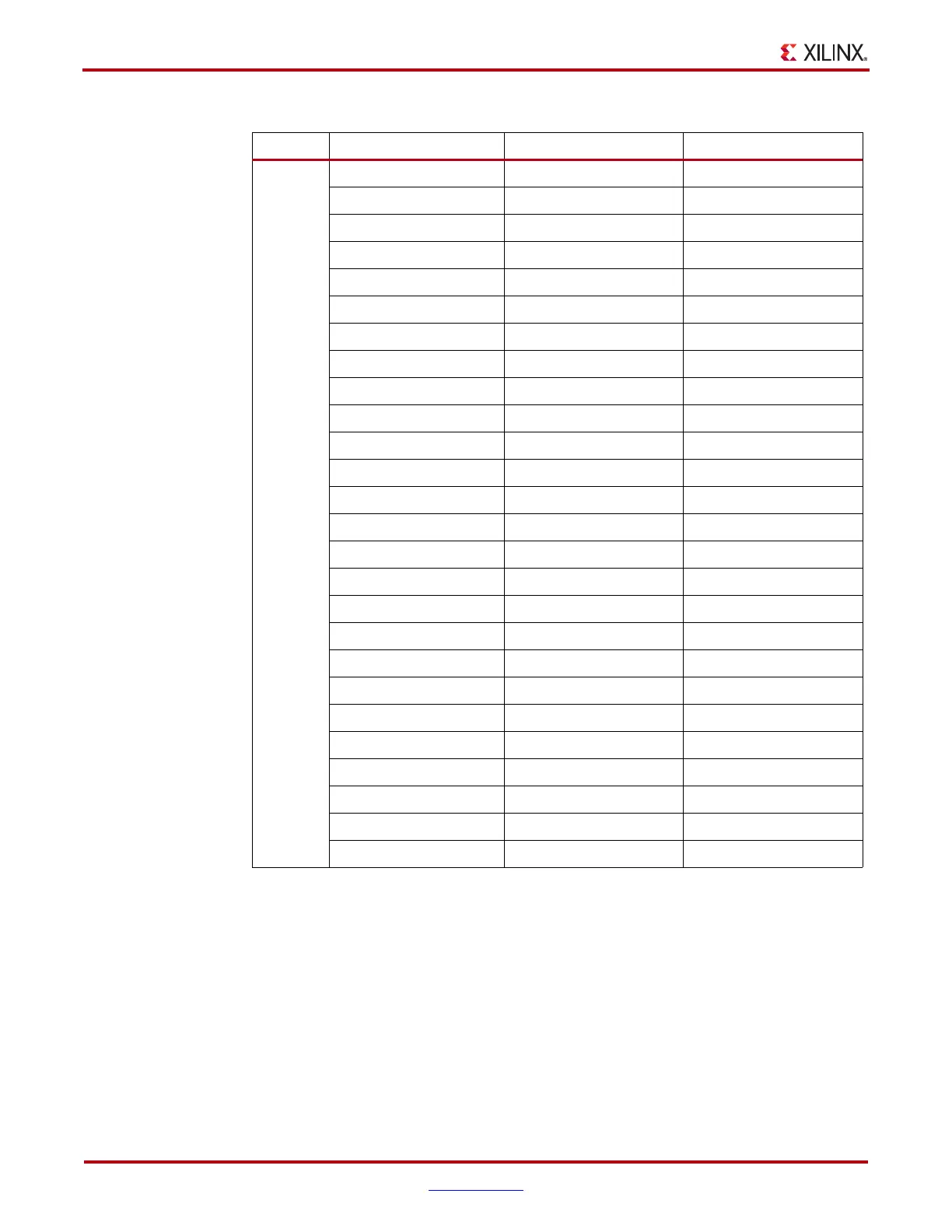

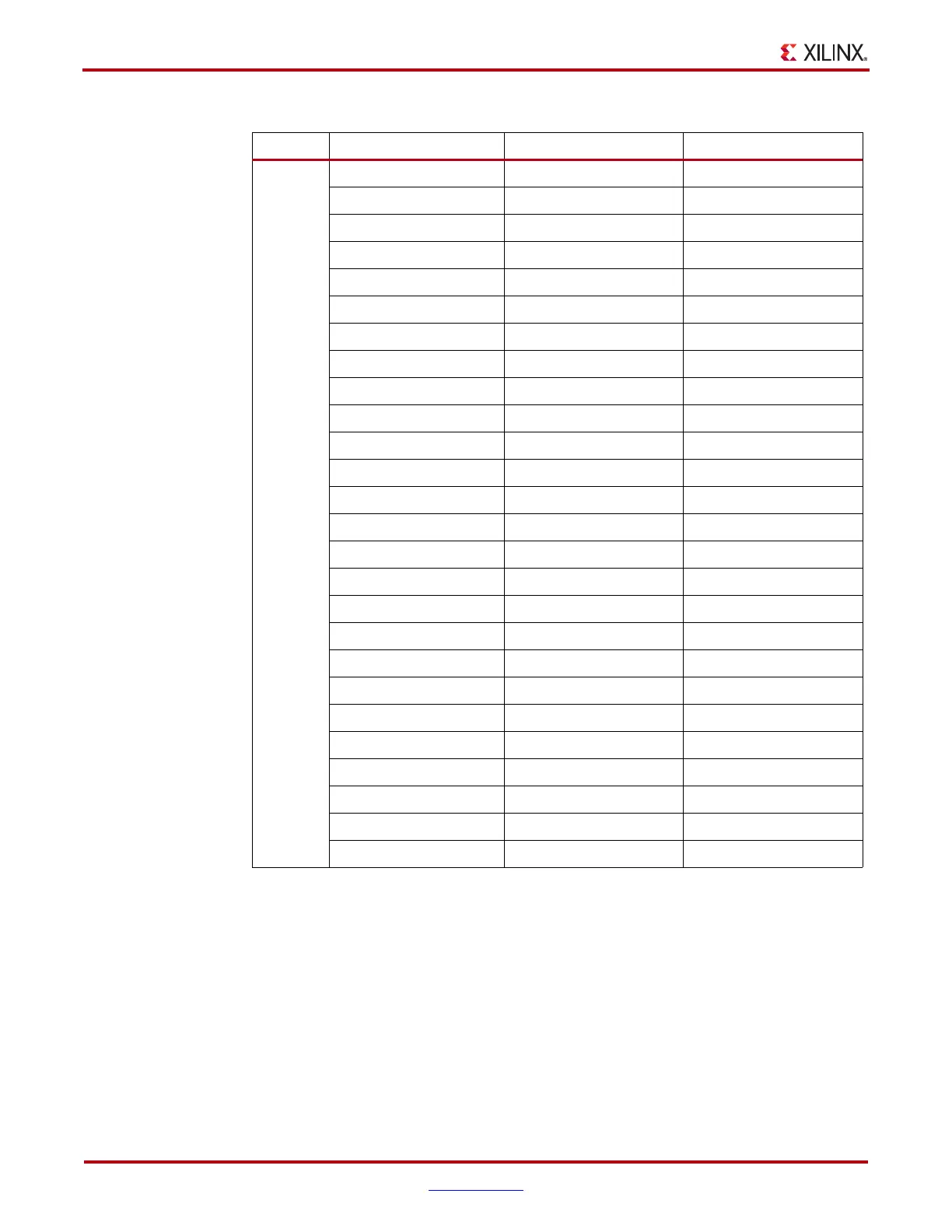

Chapter 6: SelectIO Resources

1.5V LVCMOS15_2_slow 20 40

LVCMOS15_4_slow 20 40

LVCMOS15_6_slow 20 40

LVCMOS15_8_slow 20 40

LVCMOS15_12_slow 20 40

LVCMOS15_16_slow 20 40

LVCMOS15_2_fast 20 40

LVCMOS15_4_fast 20 40

LVCMOS15_6_fast 20 40

LVCMOS15_8_fast 20 40

LVCMOS15_12_fast 20 40

LVCMOS15_16_fast 20 40

LVDCI_15 50 Ω 20 40

HSTL_I_15 20 40

HSTL_I_15_DCI 20 40

HSTL_II_15 20 40

HSTL_II_15_DCI 20 40

HSTL_III_15 20 40

HSTL_III_15_DCI 20 40

HSTL_IV_15 12 25

HSTL_IV_15_DCI 12 25

HSLVDCI_15 50 Ω 20 40

DIFF_HSTL_I_15 20 40

DIFF_HSTL_I_15_DCI 20 40

DIFF_HSTL_II_15 20 40

DIFF_HSTL_II_15_DCI 20 40

Table 6-40:

Maximum Number of Simultaneously Switching Outputs per Bank (Continued)

Voltage IOSTANDARD Limit per 20-pin Bank Limit per 40-pin Bank

Loading...

Loading...