328 www.xilinx.com Virtex-5 FPGA User Guide

UG190 (v5.0) June 19, 2009

Chapter 7: SelectIO Logic Resources

Module Reset - RST

The IODELAY reset signal, RST, resets the delay element to a value set by the

IDELAY_VALUE or ODELAY_VALUE attribute. If these attributes are not specified, a

value of zero is assumed. The RST signal is an active-High reset and is synchronous to the

input clock signal (C).

The control pins are summarized in Table 7-8.

Increment/Decrement Signals - CE, INC

The increment/decrement is controlled by the enable signal (CE). This interface is only

available for the IDELAY mode, when IDELAY_TYPE = VARIABLE.

As long as CE remains High, IDELAY will increment or decrement by T

IDELAYRESOLUTION

every clock (C) cycle. The state of INC determines whether IDELAY will increment or

decrement; INC = 1 increments, INC = 0 decrements, synchronously to the clock (C). If CE

is Low the delay through IDELAY will not change regardless of the state of INC.

When CE goes High, the increment/decrement operation begins on the next positive clock

cycle. When CE goes Low, the increment/decrement operation ceases on the next positive

clock cycle.

IODELAY is a wrap-around programmable delay element. When the end of the delay

element is reached (tap 63) a subsequent increment function will return to tap 0. The same

applies to the decrement function: decrementing below zero moves to tap 63. The

increment/decrement operation is summarized in Table 7-9.

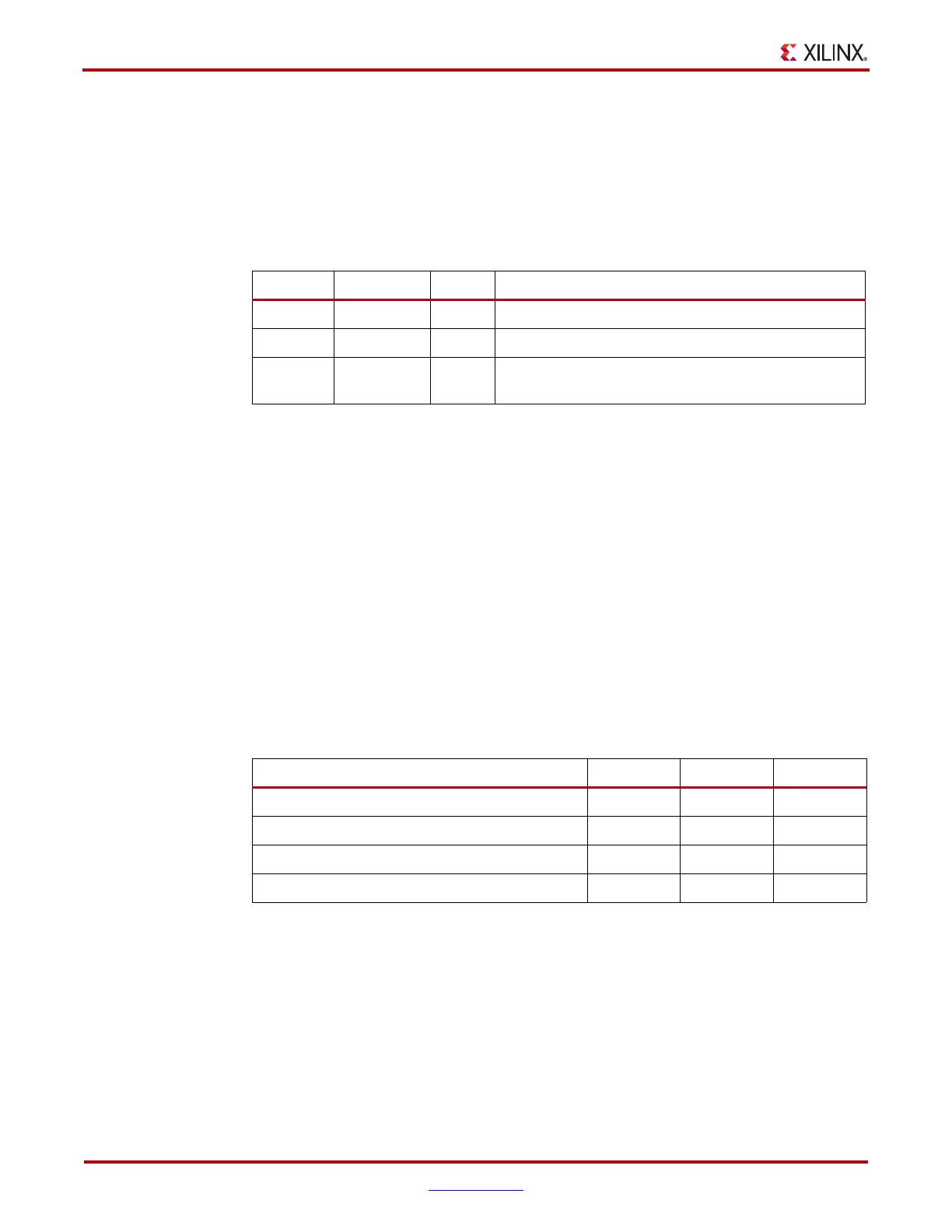

Table 7-8: Control Pin Descriptions

Pin Type Value Description

INC Input 1 Increment/decrement number of tap delays

CE Input 1 Enable increment/decrement function

RST Input 1

Reset delay element to pre-programmed value. If no

value programmed, reset to 0

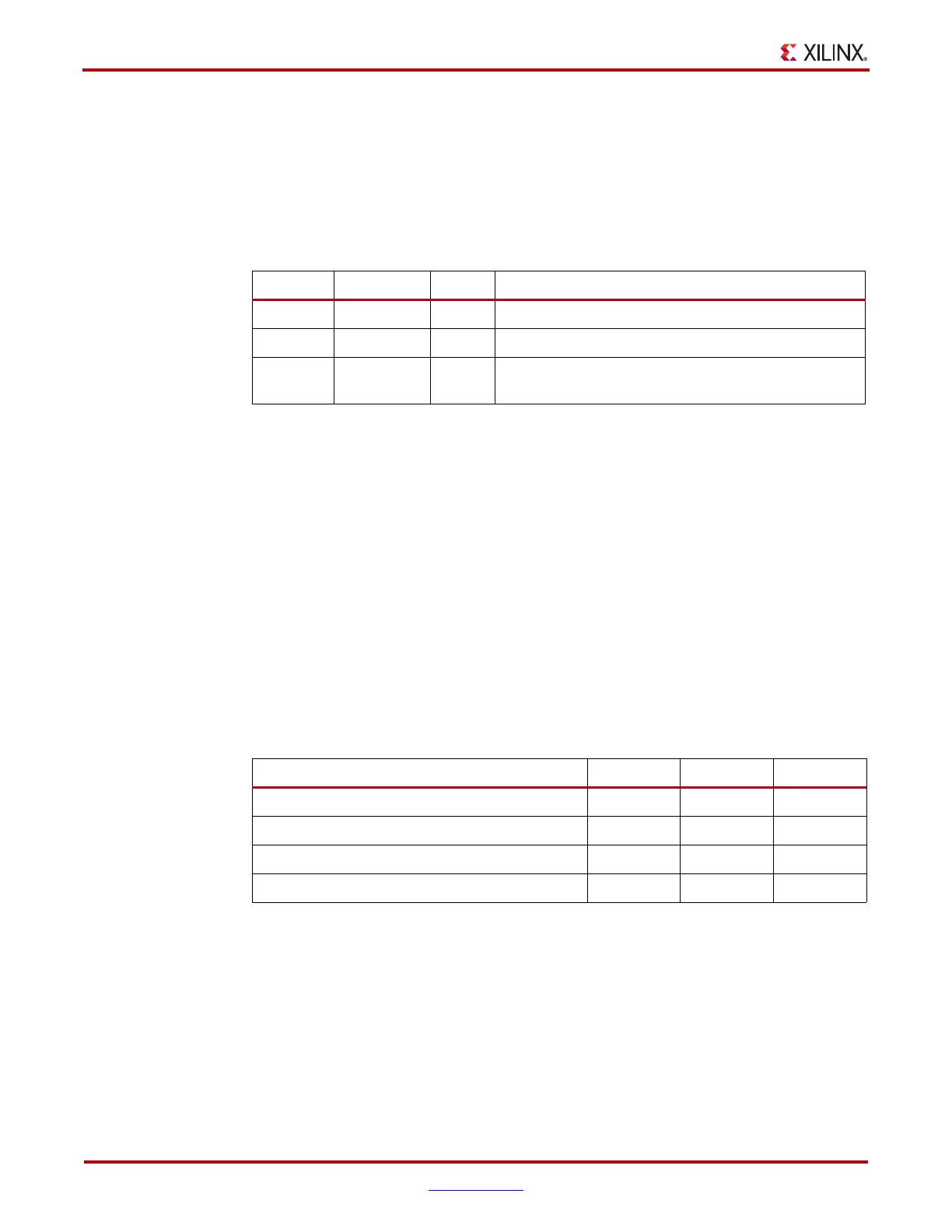

Table 7-9: Increment/Decrement Operations

Operation RST CE INC

Reset to IDELAY_VALUE 1 x x

Increment tap count 0 1 1

Decrement tap count 0 1 0

No change 0 0 x

Notes:

1. RST takes precedence over CE and INC.

Loading...

Loading...