Virtex-5 FPGA User Guide www.xilinx.com 341

UG190 (v5.0) June 19, 2009

Input/Output Delay Element (IODELAY)

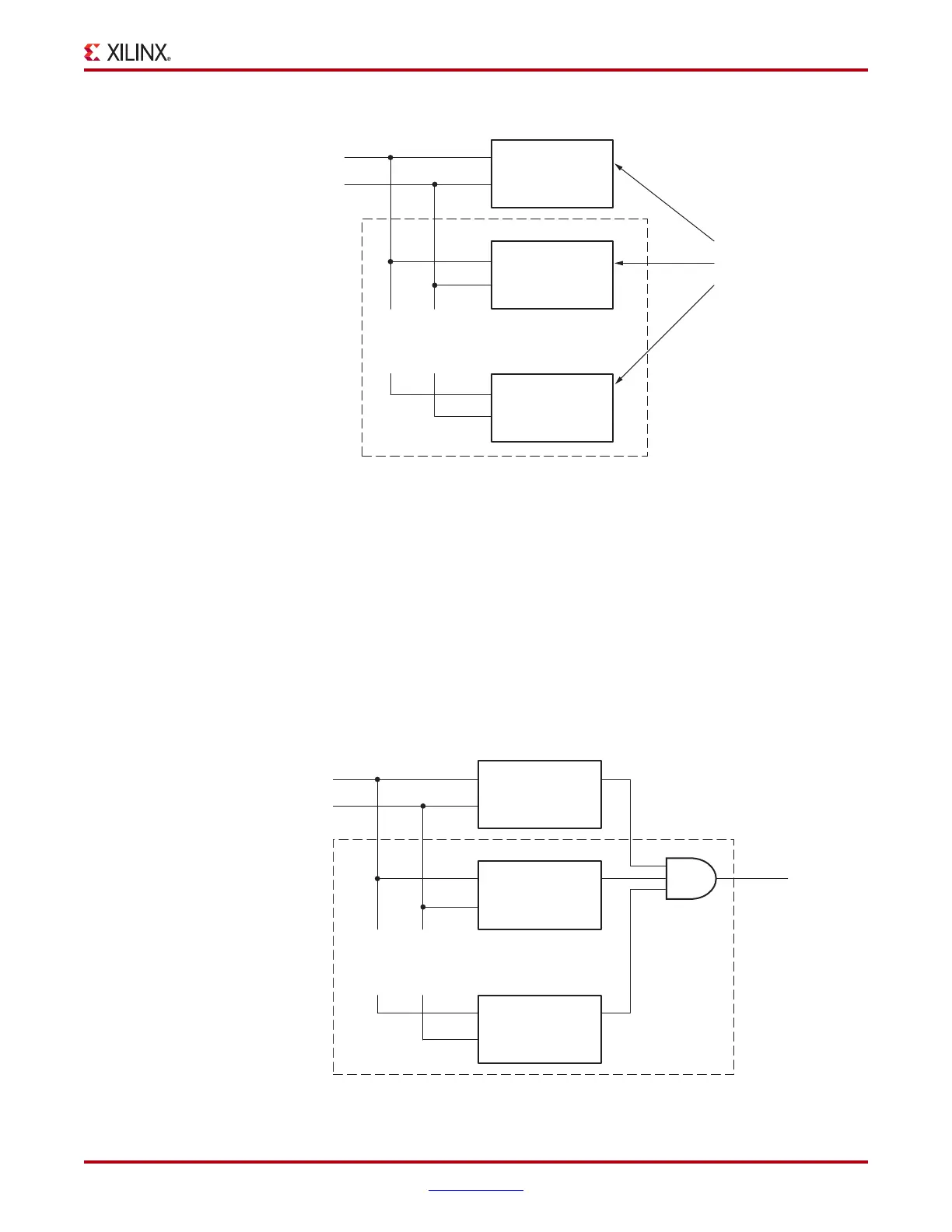

2. When RDY port is connected, an AND gate of width equal to the number of clock

regions is instantiated and the RDY output ports from the instantiated and replicated

IDELAYCTRL instances are connected to the inputs of the AND gate. The tools assign

the signal name connected to the RDY port of the instantiated IDELAYCTRL instance

to the output of the AND gate.

The VHDL and Verilog use models for instantiating an IDELAYCTRL primitive

without LOC constraints with the RDY port connected are provided in the Libraries

Guide.

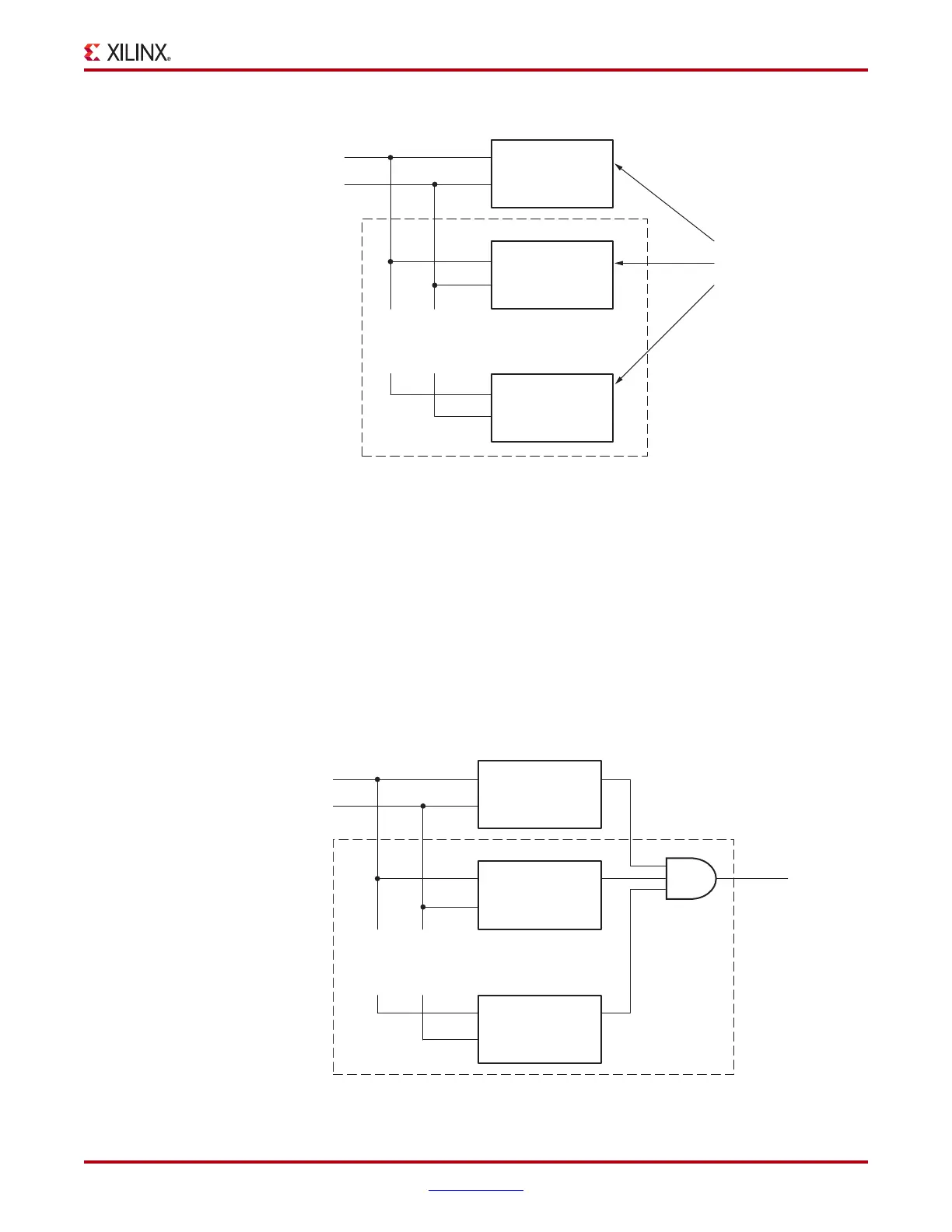

The resulting circuitry after instantiating the IDELAYCTRL components is illustrated

in Figure 7-19.

X-Ref Target - Figure 7-18

Figure 7-18: Instantiate IDELAYCTRL Without LOC Constraints - RDY Unconnected

X-Ref Target - Figure 7-19

Figure 7-19: Instantiate IDELAYCTRL Without LOC Constraints - RDY Connected

.

.

.

REFCLK

.

.

.

Replicated for

all IDELAYCTRL

sites

RST

.

.

.

RDY signal ignored

Auto-generated by

mapper tool

Instantiated by user

REFCLK RDY

RST

IDELAYCTRL

IDELAYCTRL

IDELAYCTRL

REFCLK RDY

RST

REFCLK RDY

RST

ug190_7_13_041206

REFCLK

RST

RDY

Instantiated by user

REFCLK RDY

RST

IDELAYCTRL

IDELAYCTRL

IDELAYCTRL

REFCLK RDY

RST

REFCLK RDY

RST

ug190_7_14_041306

.

.

.

.

.

.

Replicated for

all IDELAYCTRL

sites

.

.

.

Auto-generated by

mapper tool

Loading...

Loading...