UG190 (v5.0) June 19, 2009 www.xilinx.com Virtex-5 FPGA User Guide

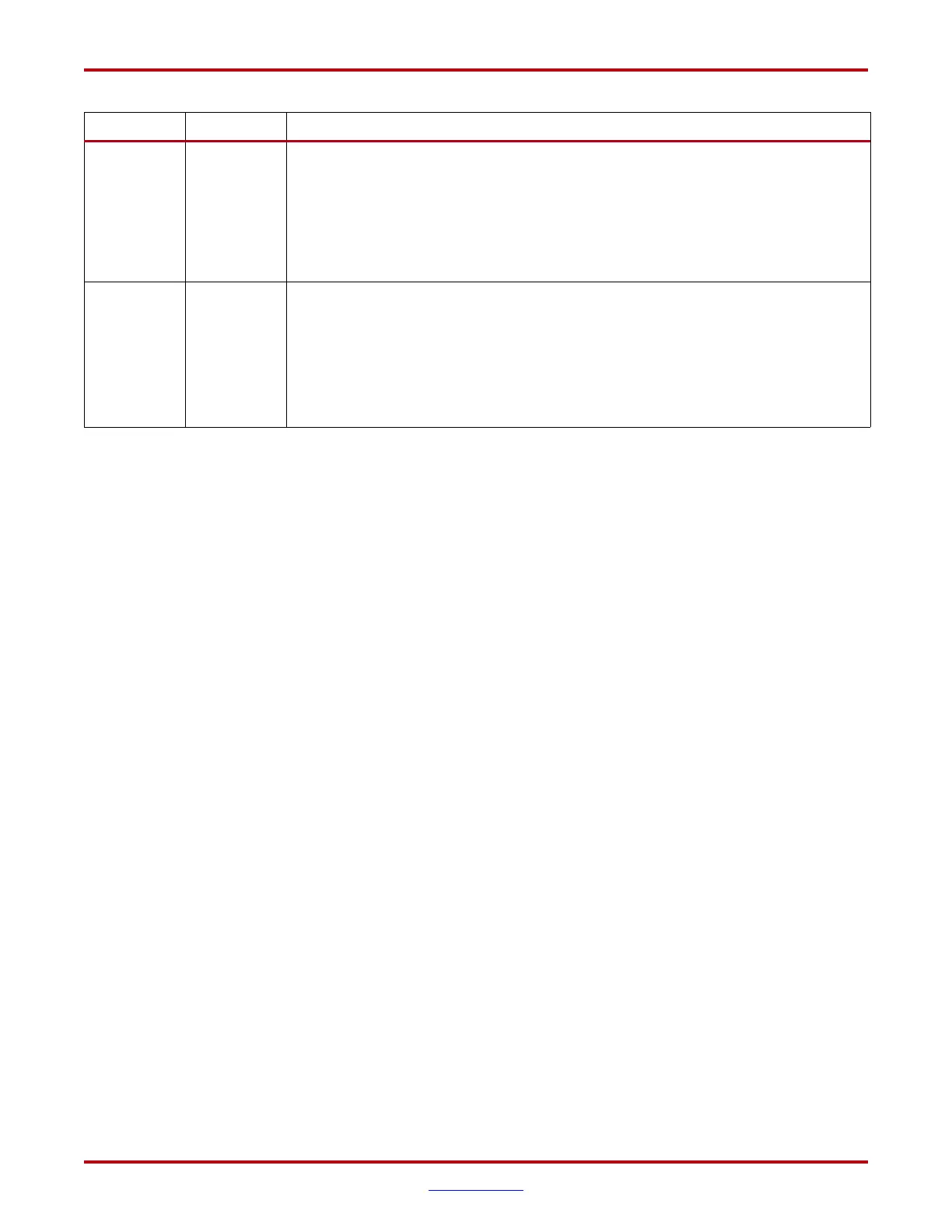

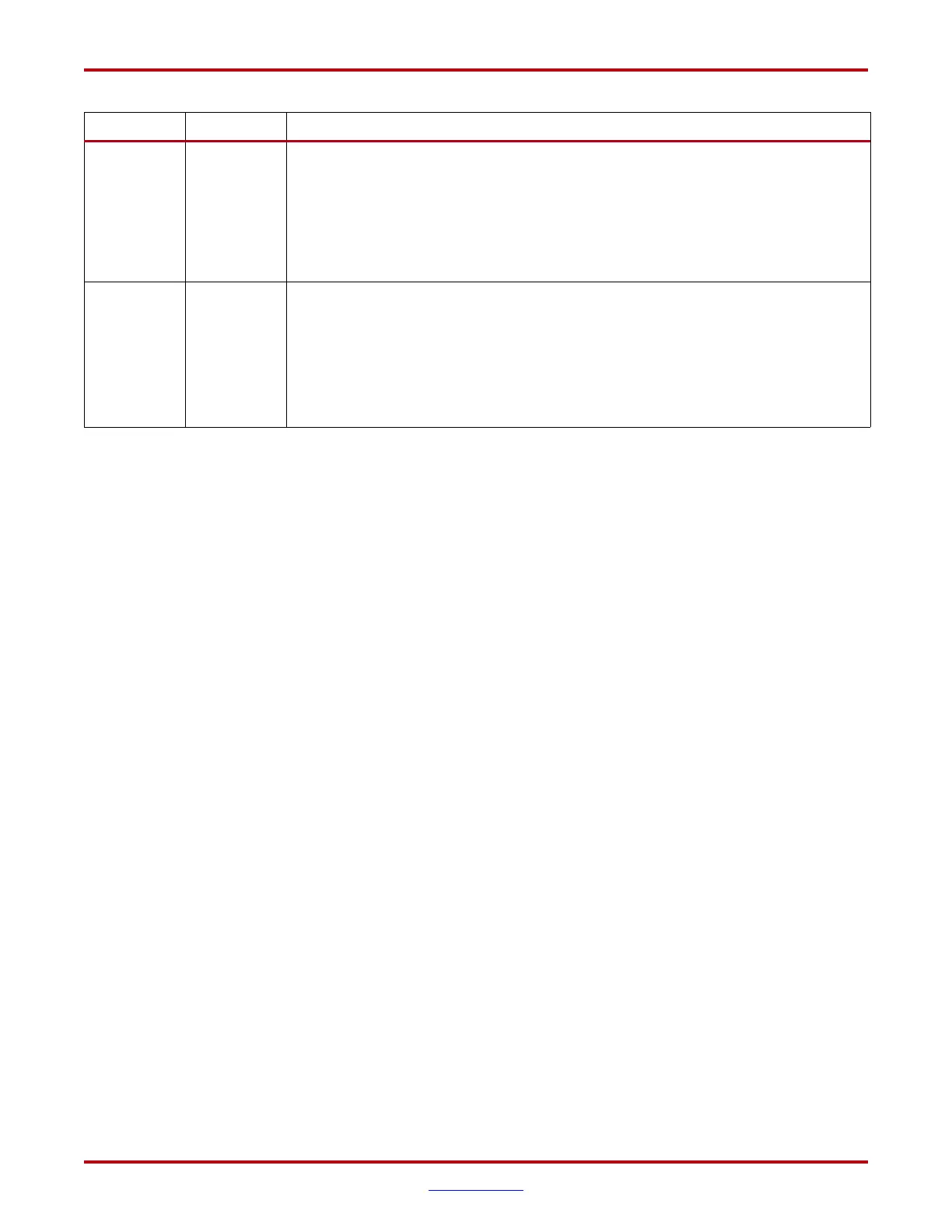

05/01/09 4.7 Chapter 3: Added 7 as one of the values of D in the last sentence of the first paragraph of

“Determine the Input Frequency,” page 95. Updated waveform 1 in Figure 3-10,

page 105.

Chapter 4: In the second paragraph of “Write Modes,” page 117, rephrased the second

paragraph. Changed “Clock Cycle Latency” to “Write/Read Cycle Latency” in

Table 4-16, page 145. In “ECC Modes Overview,” page 159, changed READ_FIRST to

NO_CHANGE in the last bullet of the section.

06/19/09 5.0 Chapter 1: Updated instances of BUFGMUX_VIRTEX4 to BUFGMUX_CTRL throughout

chapter. Clarified global and local clocking in first paragraph of “Global and Regional

Clocks,” page 25.

Chapter 2: Updated Dynamic Reconfiguration description in “DCM Summary,” page 48

to remove “different phase shift” as an attribute changeable via dynamic

reconfiguration.

Chapter 3: Updated definition of LOCKED pin in Table 3-3, page 96.

Date Version Revision

Loading...

Loading...