Virtex-5 FPGA User Guide www.xilinx.com 283

UG190 (v5.0) June 19, 2009

Specific Guidelines for I/O Supported Standards

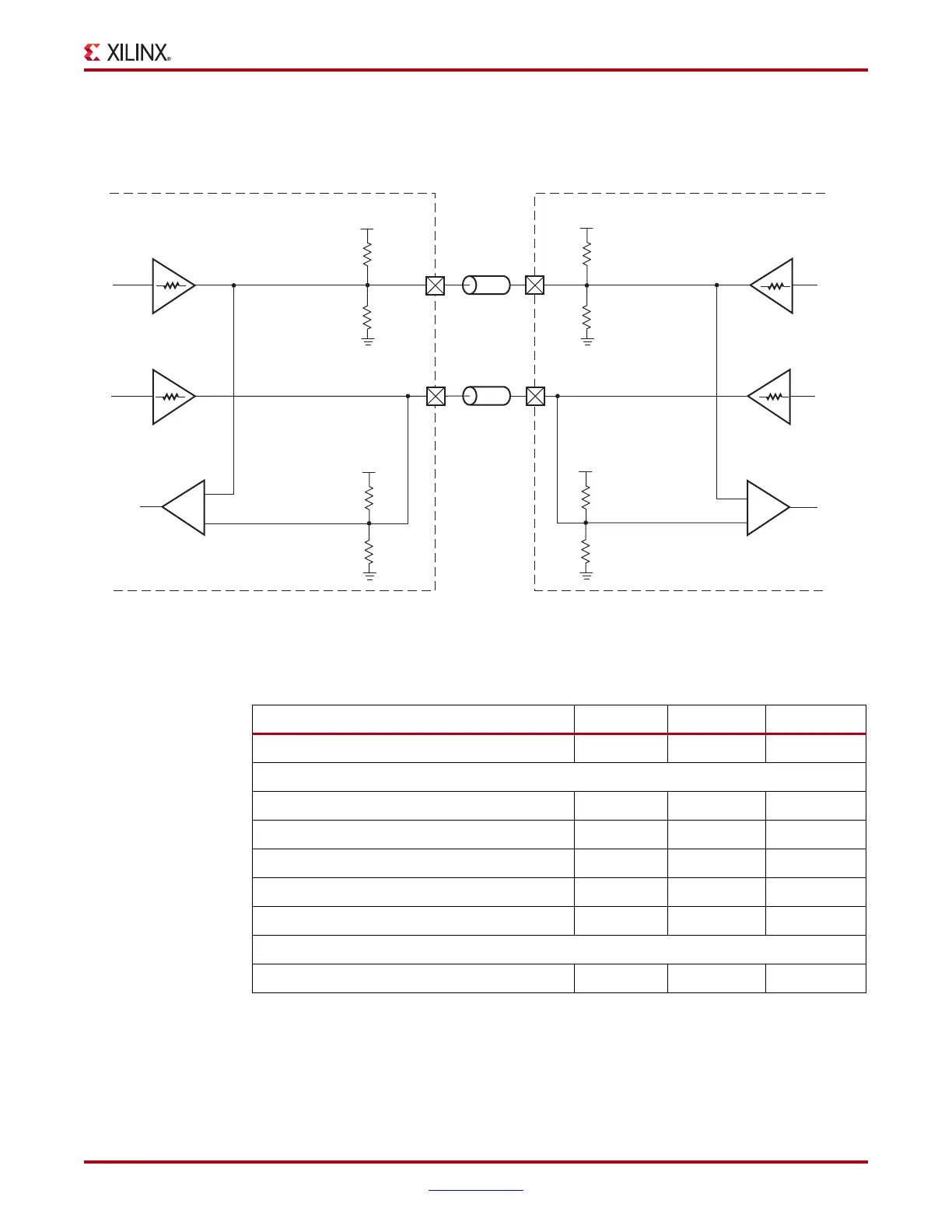

Figure 6-75 shows a sample circuit illustrating a valid termination technique for

differential SSTL2 Class II (2.5V) with bidirectional DCI termination.

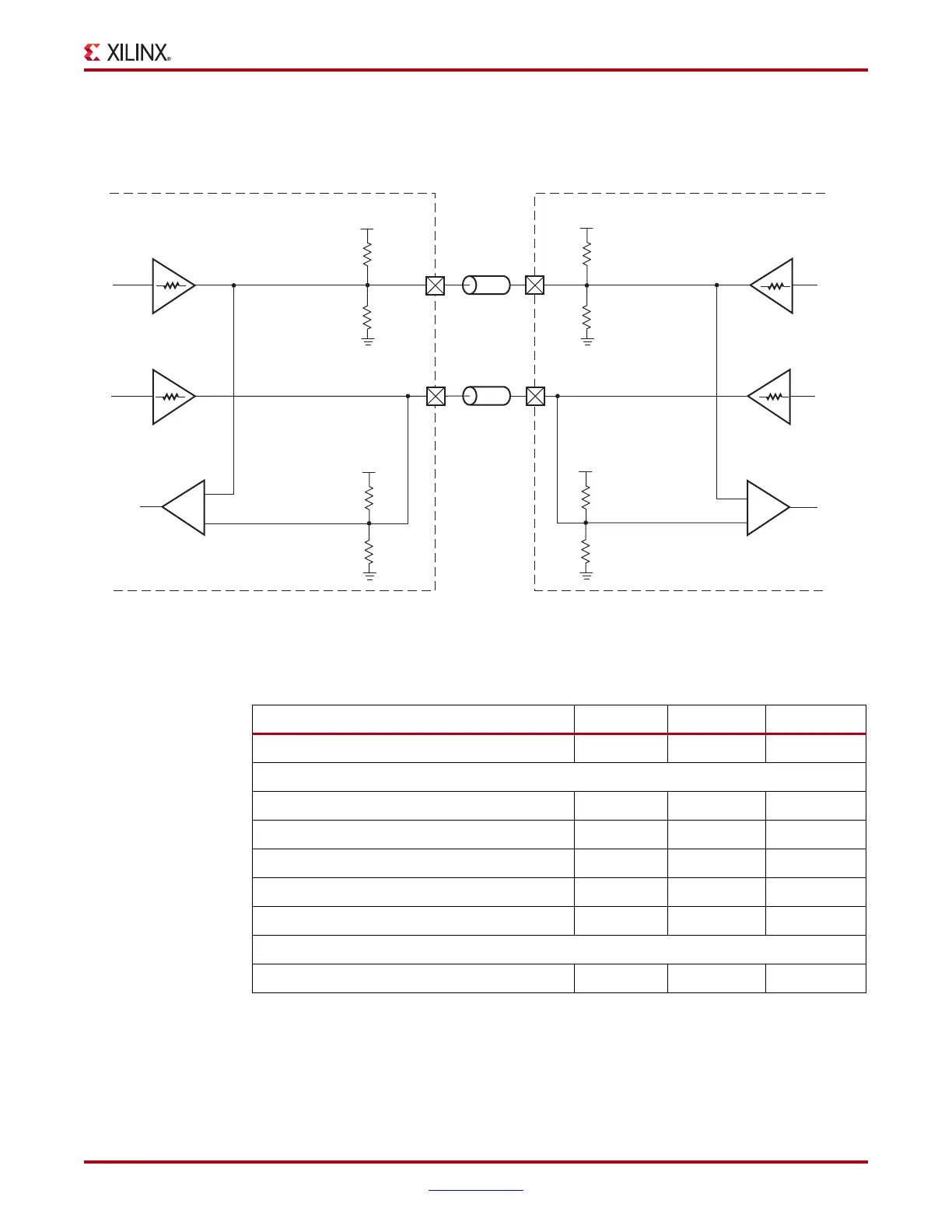

Table 6-31 lists the differential SSTL2 Class II DC voltage specifications.

X-Ref Target - Figure 6-75

Figure 6-75: Differential SSTL2 (2.5V) Class II with DCI Bidirectional Termination

Z

0

IOB

IOB

DIFF_SSTL2_II_DCI DIFF_SSTL2_II_DCI

V

CCO

= 2.5V

2R

VRP

= 2Z

0

= 100Ω

2R

VRN

= 2Z

0

= 100Ω

+

–

DCI

V

CCO

= 2.5V

2R

VRP

= 2Z

0

= 100Ω

2R

VRN

= 2Z

0

= 100Ω

DIFF_SSTL2_II_DCI

ug190_6_71_041106

Z

0

DIFF_SSTL2_II_DCI

DIFF_SSTL2_II_DCI DIFF_SSTL2_II_DCI

V

CCO

= 2.5V

2R

VRP

= 2Z

0

= 100Ω

2R

VRN

= 2Z

0

= 100Ω

+

–

V

CCO

= 2.5V

2R

VRP

= 2Z

0

= 100Ω

2R

VRN

= 2Z

0

= 100Ω

R

0

= 25Ω

R

0

= 25Ω

R

0

= 25Ω

R

0

= 25Ω

Table 6-31: Differential SSTL2 Class II DC Voltage Specifications

Min Typ Max

V

CCO

2.3 2.5 2.7

Input Parameters

V

TT

–V

CCO

× 0.5 –

V

IN

(DC)

(1)

–0.30 – V

CCO

+0.30

V

ID

(DC)

(2)

0.3 – V

CCO

+0.60

V

ID

(AC) 0.62 – V

CCO

+0.60

V

IX

(AC)

(3)

0.95 – 1.55

Output Parameters

V

OX

(AC)

(4)

1.0 – 1.5

Notes:

1. V

IN

(DC) specifies the allowable DC excursion of each differential input.

2. V

ID

(DC) specifies the input differential voltage required for switching.

3. V

IX

(AC) indicates the voltage where the differential input signals must cross.

4. V

OX

(AC) indicates the voltage where the differential output signals must cross.

Loading...

Loading...