Virtex-5 FPGA User Guide www.xilinx.com 31

UG190 (v5.0) June 19, 2009

Global Clocking Resources

Table 1-4 summarizes the attributes for the BUFGCTRL primitive.

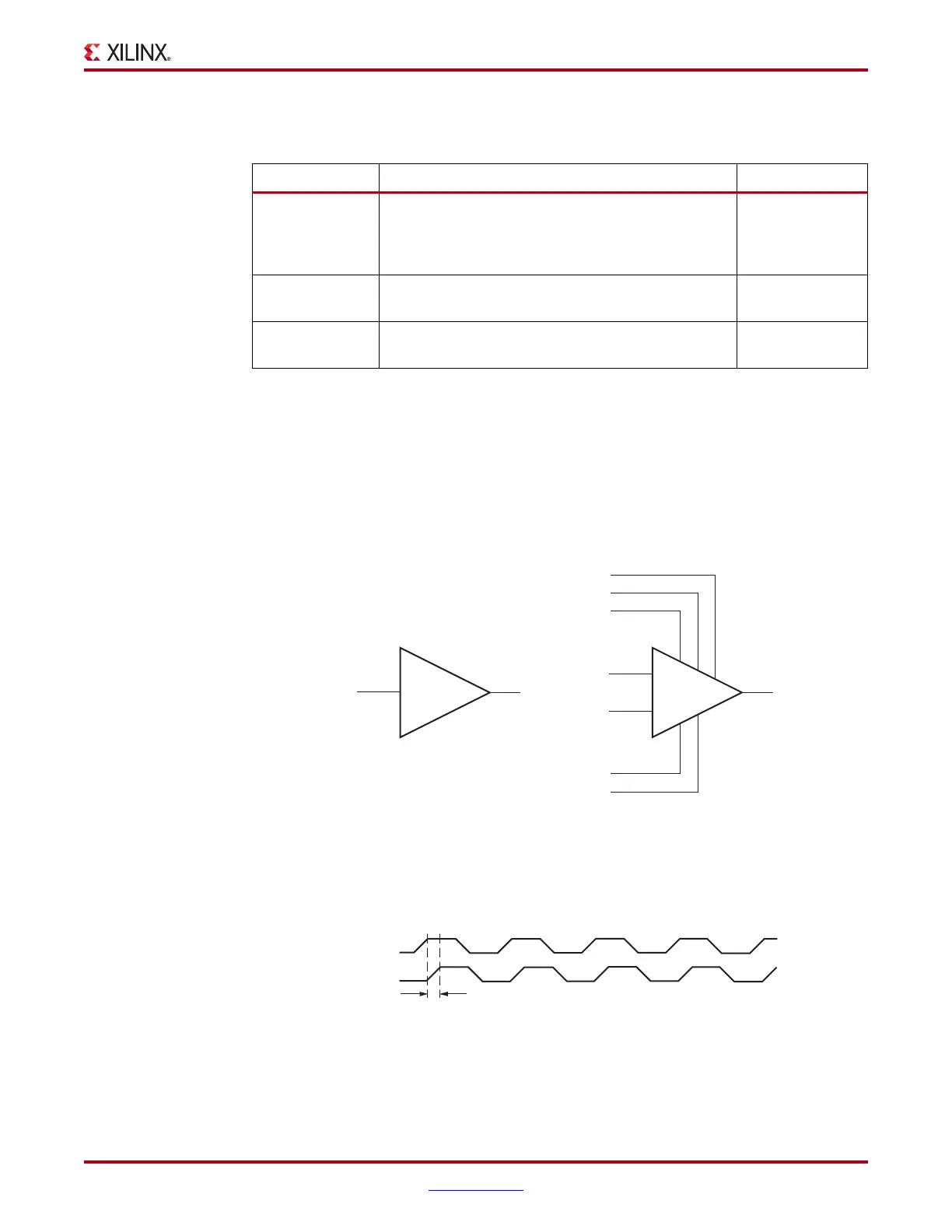

BUFG

BUFG is simply a clock buffer with one clock input and one clock output. This primitive is

based on BUFGCTRL with some pins connected to logic High or Low. Figure 1-3 illustrates

the relationship of BUFG and BUFGCTRL. A LOC constraint is available for BUFG.

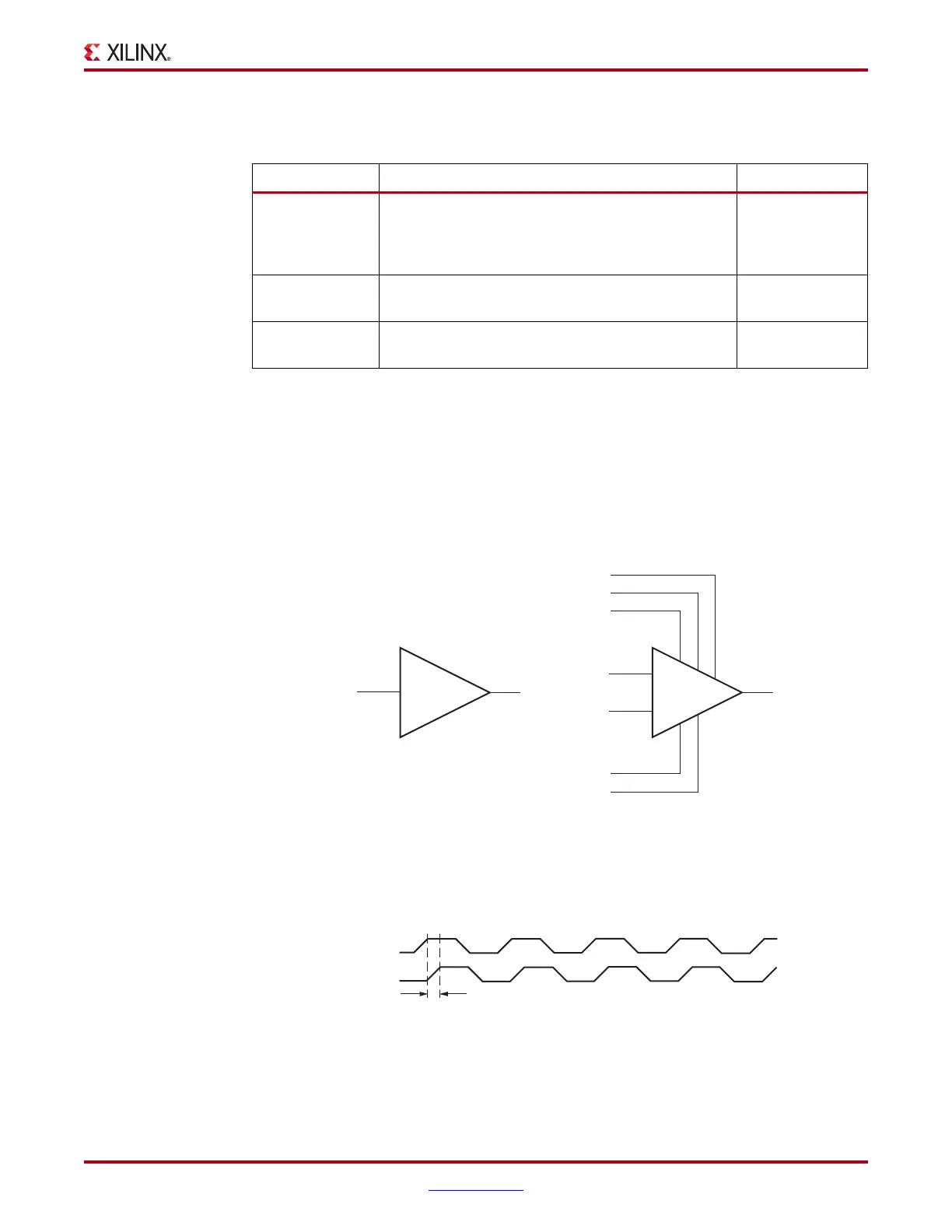

The output follows the input as shown in the timing diagram in Figure 1-4.

Table 1-4: BUFGCTRL Attributes

Attribute Name Description Possible Values

INIT_OUT Initializes the BUFGCTRL output to the specified

value after configuration. Sets the positive or

negative edge behavior. Sets the output level when

changing clock selection.

0 (default), 1

PRESELECT_I0 If TRUE, BUFGCTRL output uses the I0 input after

configuration

(1)

FALSE (default),

TRUE

PRESELECT_I1 If TRUE, BUFGCTRL output uses the I1 input after

configuration

(1)

FALSE (default),

TRUE

Notes:

1. Both PRESELECT attributes cannot be TRUE at the same time.

2. The LOC constraint is available.

X-Ref Target - Figure 1-3

Figure 1-3: BUFG as BUFGCTRL

X-Ref Target - Figure 1-4

Figure 1-4: BUFG Timing Diagram

IGNORE1

IGNORE0

CE1

CE0

S1

S0

I1

I0

O

BUFG

ug190_1_03_032206

V

DD

GND

V

DD

V

DD

V

DD

I

O

I

GND

GND

BUFG(I)

BUFG(O)

T

BCCKO_O

ug190_1_04_032206

Loading...

Loading...