UG190 (v5.0) June 19, 2009 www.xilinx.com Virtex-5 FPGA User Guide

12/11/07 3.2 Chapter 1: Revised description in “Clock Gating for Power Savings,” page 26. Added the

XC5VLX20T, XC5VLX155, and XC5VLX155T devices to Table 1-5.

Chapter 2: Added the XC5VLX20T, XC5VLX155, and XC5VLX155T devices to Table 2-1.

Chapter 3: Revised “Clock Network Deskew,” page 93. Removed note 2 and revised

descriptions of CLKFBOUT and DEN in Table 3-3, page 96. Revised allowed value of

CLKOUT[0:5]_PHASE and CLKFBOUT_MULT description in Table 3-4, page 98.

Revised Figure 3-13 and Figure 3-14 including waveforms.

Chapter 5: Added the XC5VLX20T, XC5VLX155, and XC5VLX155T devices to Table 5-2.

Chapter 6: Clarified discussion of cascading across CMT tiles in “DCI Cascading.”

Changed the split termination to V

TT

= 0.9V in Figure 6-84, page 292.

Chapter 7: Added to the descriptions of the “HIGH_PERFORMANCE_MODE

Attribute,” and the “SIGNAL_PATTERN Attribute,” page 330 including Table 7-10.

Revised description in “Instantiating IDELAYCTRL Without LOC Constraints,” page

340.

Chapter 8: Complete rewrite of the chapter. Many changes to descriptions, tables, and

figures.

02/05/08 3.3 Chapter 1: Updated discussion under “I/O Clock Buffer - BUFIO” on page 41.

Chapter 3: Revised LOCKED description in Table 3-3, page 96. Revised discussion under

“Detailed VCO and Output Counter Waveforms,” page 103.

Chapter 5: Updated description of Figure 5-17.

Chapter 7: Updated description under “Clock Input - C” on page 327. Updated default

value to TRUE for HIGH_PERFORMANCE_MODE in Table 7-10, page 329.

Chapter 8: Revised TRISTATE_WIDTH in Table 8-7, page 374. Updated discussion

under “TRISTATE_WIDTH Attribute” and added section on “OSERDES Clocking

Methods,” page 375.

03/31/08 4.0 Added the FXT platform to Table 1-5, Table 2-1, and Table 5-2.

Revised timing event description under Figure 1-21, page 44.

Revised “Dynamic Reconfiguration,” page 73 to remove adjustment of PHASE_SHIFT.

Added CLKOUT[0:5]_DESKEW_ADJUST to Table 3-4, page 98.

Corrected READ_WIDTH_B = 9 to WRITE_WIDTH_B = 9 in the block RAM usage rules

on page 114.

Revised “High-Speed Clock for Strobe-Based Memory Interfaces - OCLK,” page 357.

Corrected BITSLIP_ENABLE value from string to boolean in “ISERDES_NODELAY

Attributes,” page 358.

04/25/08 4.1 Added the XC5VSX240T to Table 1-5, Table 2-1, and Table 5-2.

Revised Figure 1-21, page 44.

Removed a pad notation from the ODDR output of Figure 2-9.

Removed the BUFG on the output of Figure 2-10.

Updated CLKOUT[0:5]_DESKEW_ADJUST description in Table 3-4, page 98.

Revised equations Equation 3-5 and Equation 3-6.

Updated the notes in Table 4-16, page 145.

Revised description of

“Instantiating IDELAYCTRL with Location (LOC) Constraints,”

page 342.

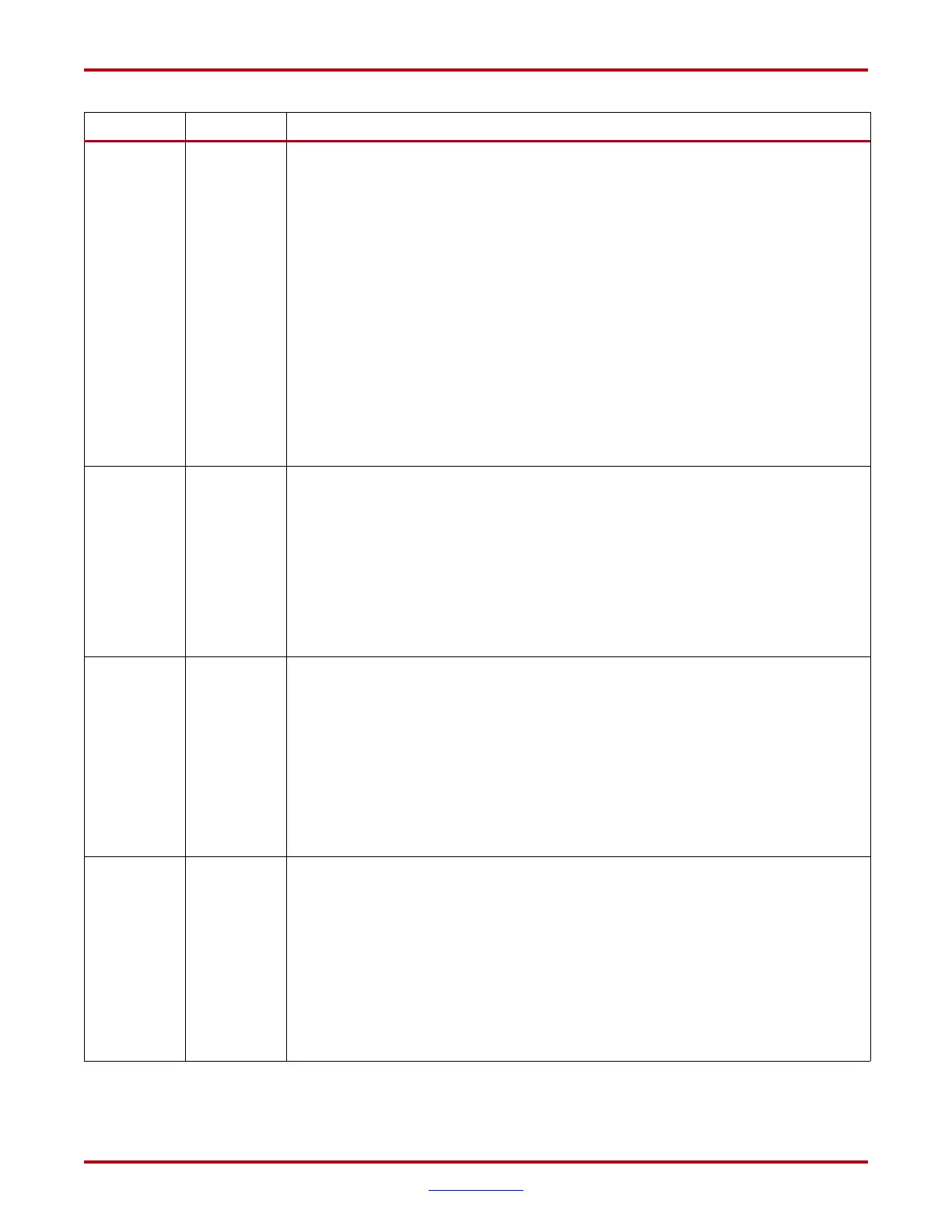

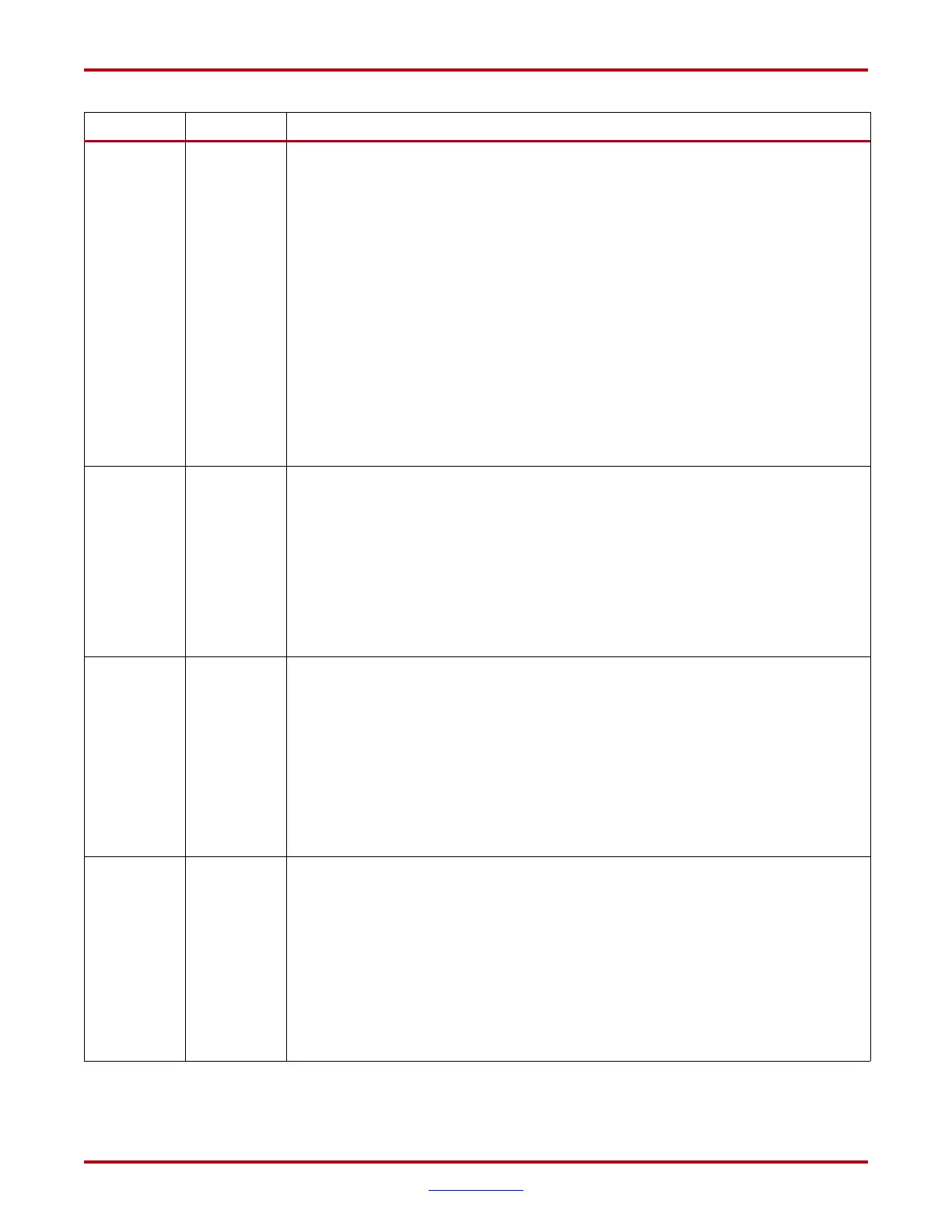

Date Version Revision

Loading...

Loading...