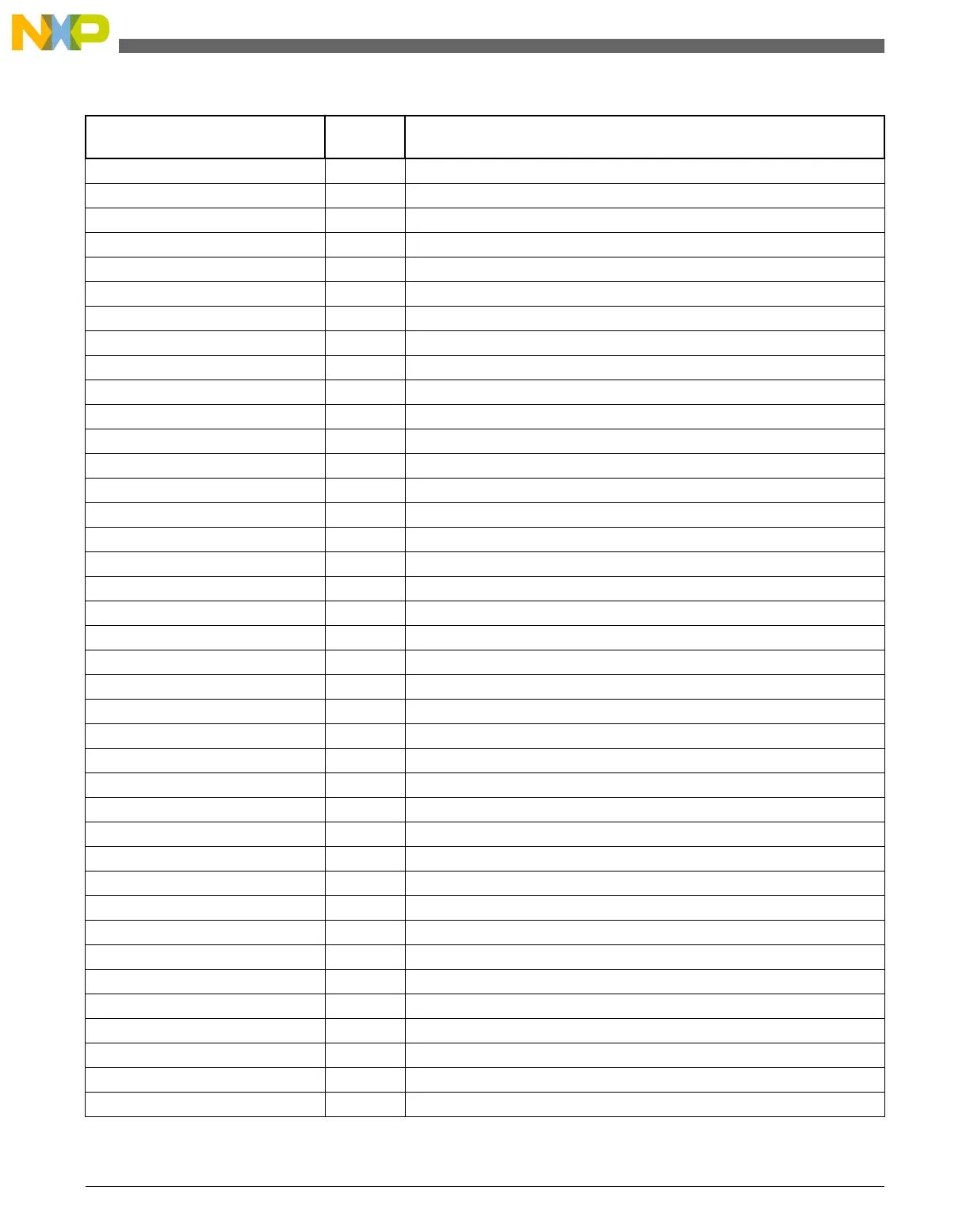

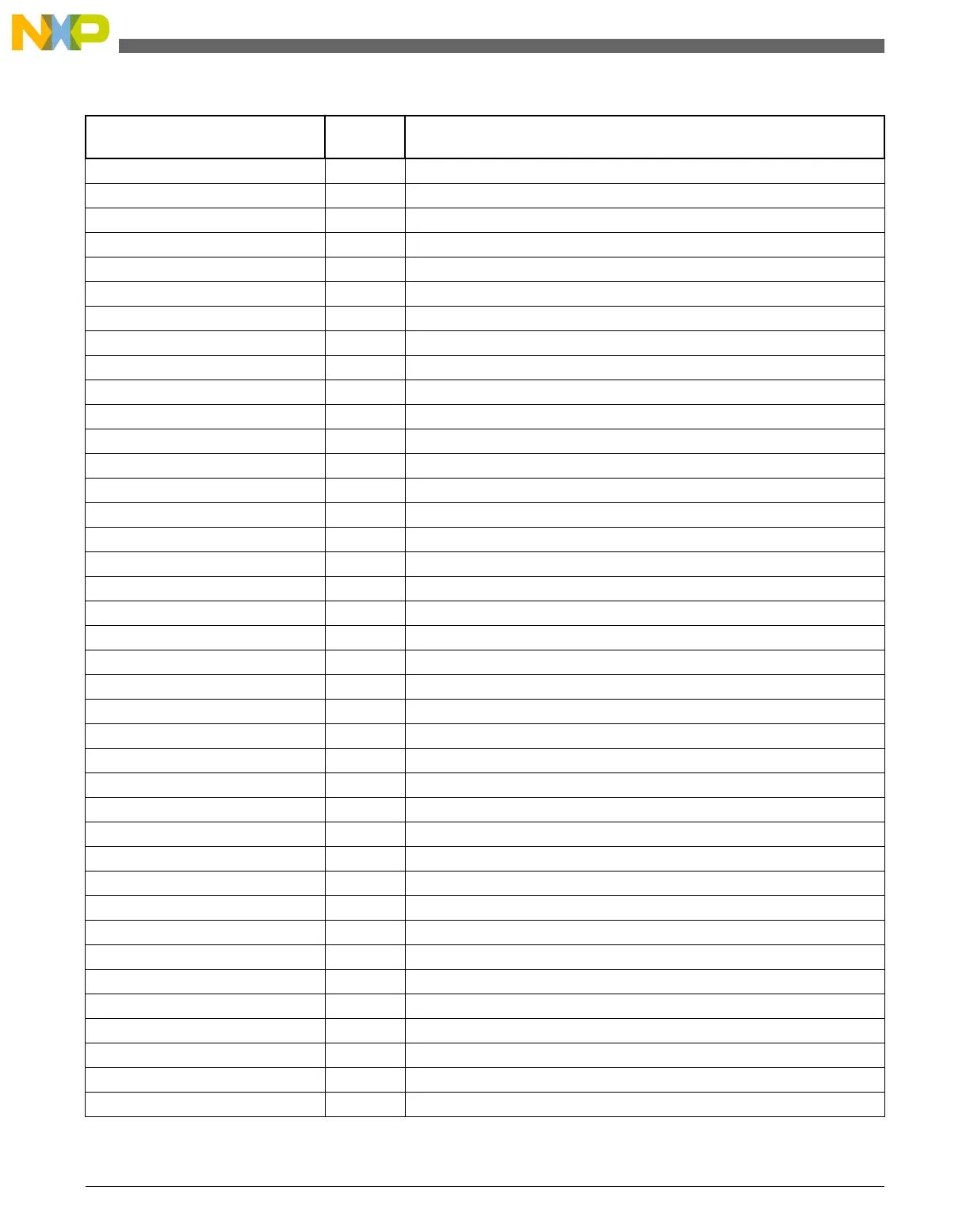

Table 4-2. Peripheral bridge 0 slot assignments (continued)

System 32-bit base address Slot

number

Module

0x4002_3000 35 —

0x4002_4000 36 —

0x4002_5000 37 —

0x4002_6000 38 —

0x4002_7000 39 —

0x4002_8000 40 —

0x4002_9000 41 —

0x4002_A000 42 —

0x4002_B000 43 —

0x4002_C000 44 —

0x4002_D000 45 —

0x4002_E000 46 —

0x4002_F000 47 —

0x4003_0000 48 —

0x4003_1000 49 —

0x4003_2000 50 —

0x4003_3000 51 —

0x4003_4000 52 —

0x4003_5000 53 —

0x4003_6000 54 —

0x4003_7000 55 Periodic interrupt timers (PIT)

0x4003_8000 56 Timer'/PWM (TPM) 0

0x4003_9000 57 Timer'/PWM (TPM) 1

0x4003_A000 58 Timer'/PWM (TPM) 2

0x4003_B000 59 Analog-to-digital converter (ADC) 0

0x4003_C000 60 —

0x4003_D000 61 Real-time clock (RTC)

0x4003_E000 62 —

0x4003_F000 63 DAC0

0x4004_0000 64 Low-power timer (LPTMR)

0x4004_1000 65 —

0x4004_2000 66 —

0x4004_3000 67 —

0x4004_4000 68 —

0x4004_5000 69 Touch sense interface (TSI)

0x4004_6000 70 —

0x4004_7000 71 SIM low-power logic

0x4004_8000 72 System integration module (SIM)

0x4004_9000 73 Port A multiplexing control

Table continues on the next page...

Peripheral bridge (AIPS-Lite) memory map

KL25 Sub-Family Reference Manual, Rev. 3, September 2012

110 Freescale Semiconductor, Inc.

Loading...

Loading...