30.4.5 DAC Control Register 1 (DACx_C1)

Address: 4003_F000h base + 22h offset = 4003_F022h

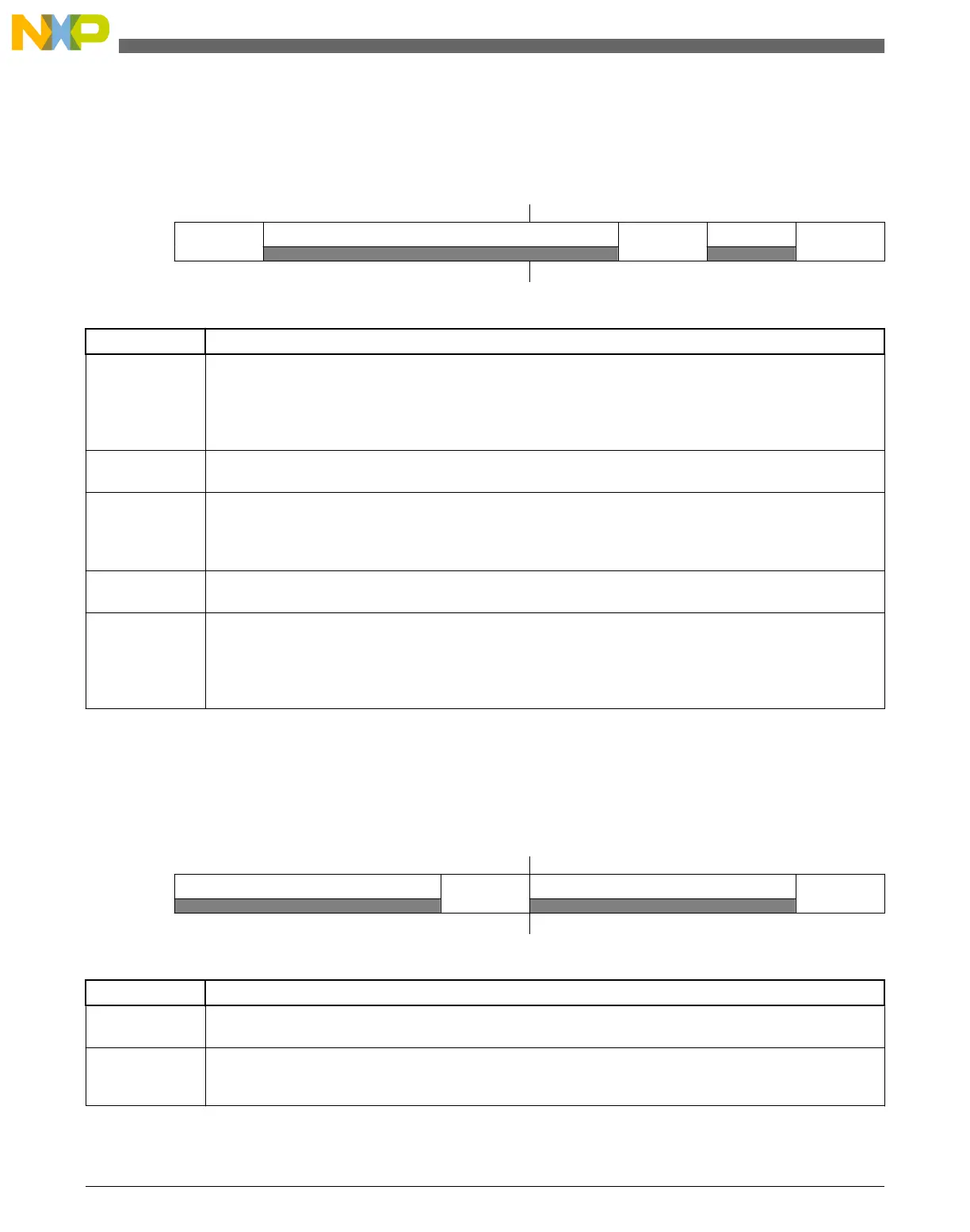

Bit 7 6 5 4 3 2 1 0

Read

DMAEN

0

DACBFMD

0

DACBFEN

Write

Reset

0 0 0 0 0 0 0 0

DACx_C1 field descriptions

Field Description

7

DMAEN

DMA Enable Select

0 DMA is disabled.

1 DMA is enabled. When DMA is enabled, the DMA request will be generated by original interrupts. The

interrupts will not be presented on this module at the same time.

6–3

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

2

DACBFMD

DAC Buffer Work Mode Select

0 Normal mode

1 One-Time Scan mode

1

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

0

DACBFEN

DAC Buffer Enable

0 Buffer read pointer is disabled. The converted data is always the first word of the buffer.

1 Buffer read pointer is enabled. The converted data is the word that the read pointer points to. It means

converted data can be from any word of the buffer.

30.4.6 DAC Control Register 2 (DACx_C2)

Address: 4003_F000h base + 23h offset = 4003_F023h

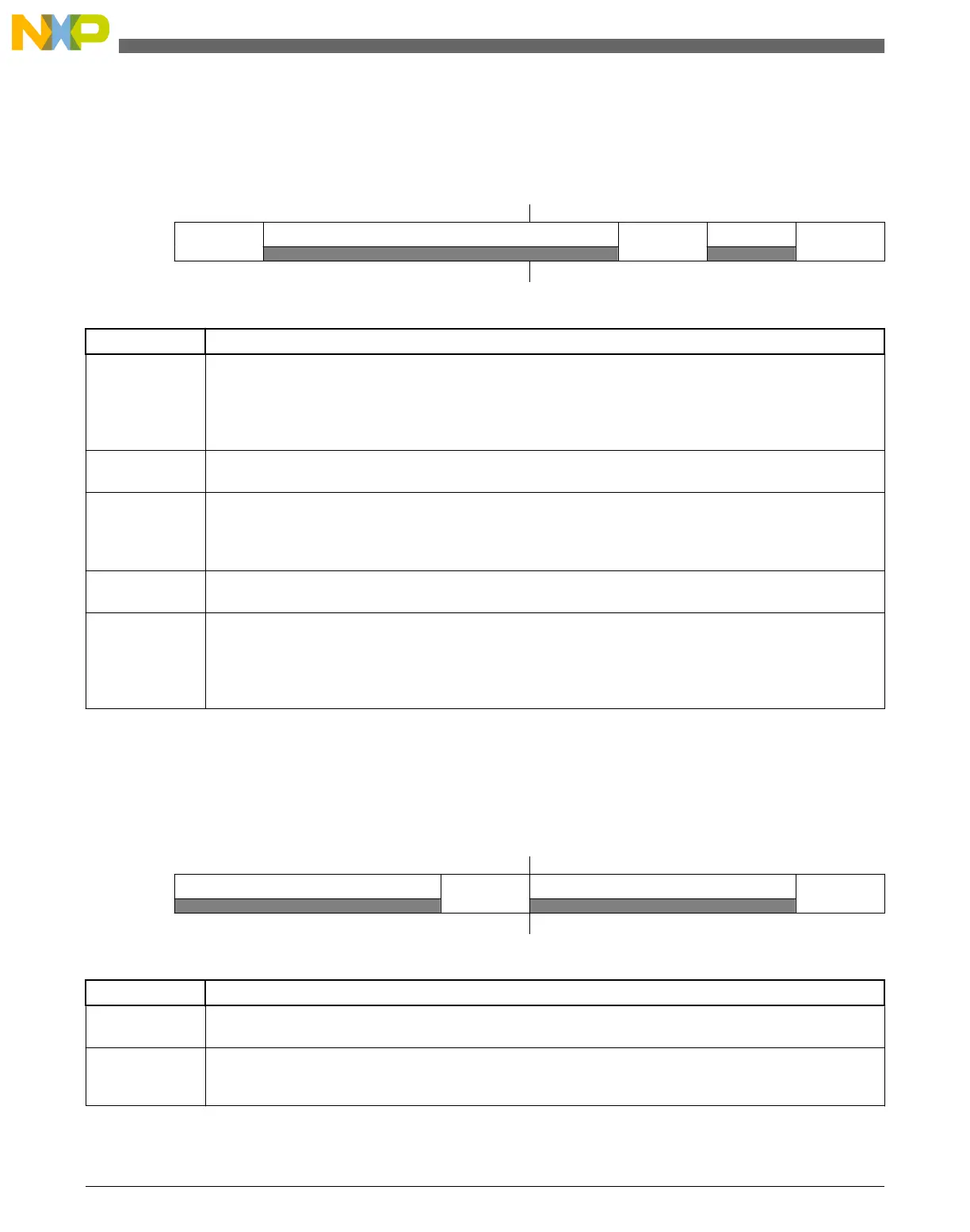

Bit 7 6 5 4 3 2 1 0

Read 0

DACBFRP

0

DACBFUP

Write

Reset

0 0 0 0 0 0 0 1

DACx_C2 field descriptions

Field Description

7–5

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

4

DACBFRP

DAC Buffer Read Pointer

Keeps the current value of the buffer read pointer.

Table continues on the next page...

Memory map/register definition

KL25 Sub-Family Reference Manual, Rev. 3, September 2012

542 Freescale Semiconductor, Inc.

Loading...

Loading...