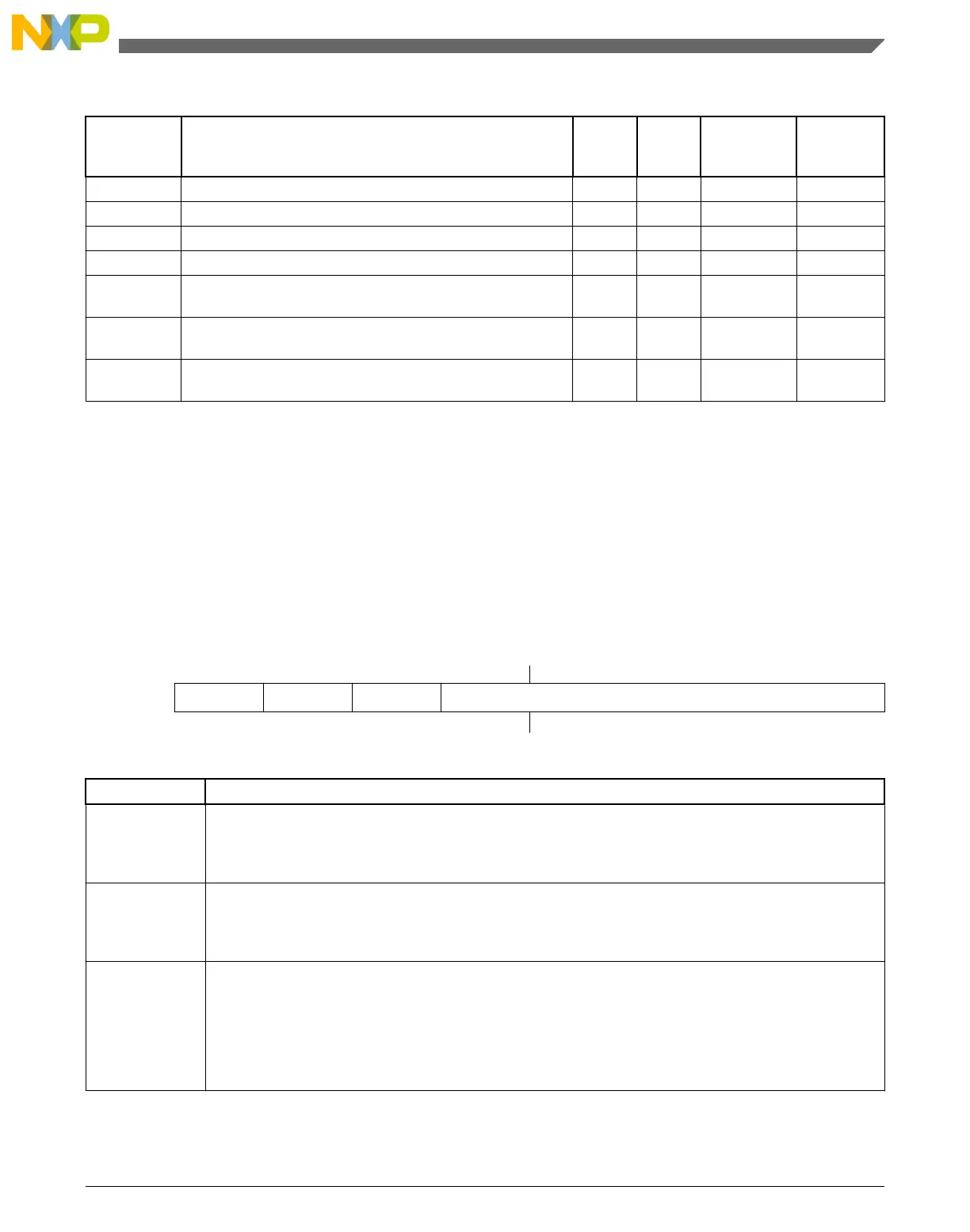

UART memory map (continued)

Absolute

address

(hex)

Register name

Width

(in bits)

Access Reset value

Section/

page

4006_A005 UART Status Register 2 (UART0_S2) 8 R/W 00h 39.2.6/731

4006_A006 UART Control Register 3 (UART0_C3) 8 R/W 00h 39.2.7/733

4006_A007 UART Data Register (UART0_D) 8 R/W 00h 39.2.8/734

4006_A008 UART Match Address Registers 1 (UART0_MA1) 8 R/W 00h 39.2.9/735

4006_A009 UART Match Address Registers 2 (UART0_MA2) 8 R/W 00h

39.2.10/

736

4006_A00A UART Control Register 4 (UART0_C4) 8 R/W 0Fh

39.2.11/

736

4006_A00B UART Control Register 5 (UART0_C5) 8 R/W 00h

39.2.12/

737

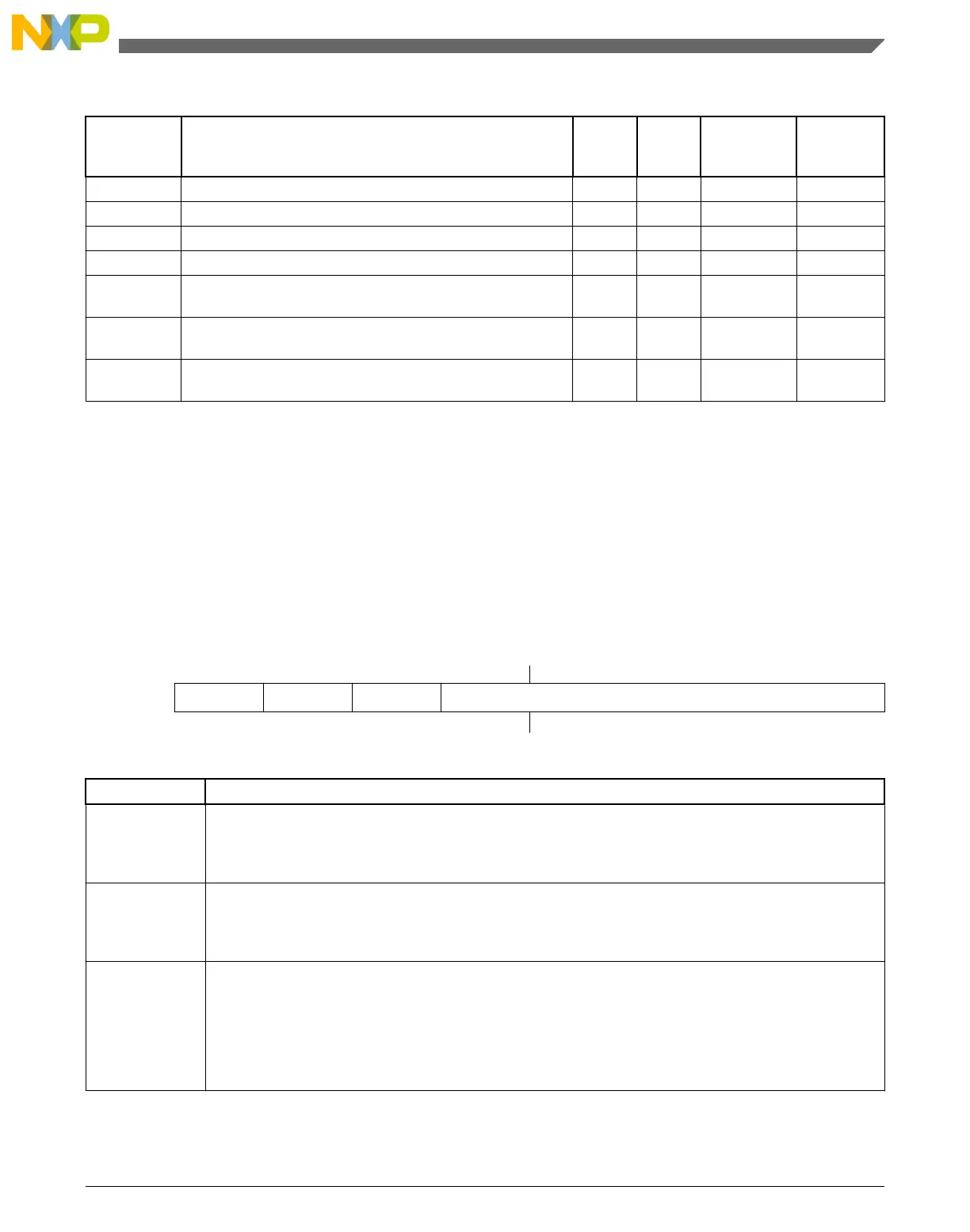

39.2.1 UART Baud Rate Register High (UARTx_BDH)

This register, along with UART _BDL, controls the prescale divisor for UART baud rate

generation. The 13-bit baud rate setting [SBR12:SBR0] should only be updated when the

transmitter and receiver are both disabled.

Address: Base address + 0h offset

Bit 7 6 5 4 3 2 1 0

Read

LBKDIE RXEDGIE SBNS SBR

Write

Reset

0 0 0 0 0 0 0 0

UARTx_BDH field descriptions

Field Description

7

LBKDIE

LIN Break Detect Interrupt Enable (for LBKDIF)

0 Hardware interrupts from UART _S2[LBKDIF] disabled (use polling).

1 Hardware interrupt requested when UART _S2[LBKDIF] flag is 1.

6

RXEDGIE

RX Input Active Edge Interrupt Enable (for RXEDGIF)

0 Hardware interrupts from UART _S2[RXEDGIF] disabled (use polling).

1 Hardware interrupt requested when UART _S2[RXEDGIF] flag is 1.

5

SBNS

Stop Bit Number Select

SBNS determines whether data characters are one or two stop bits. This bit should only be changed when

the transmitter and receiver are both disabled.

0 One stop bit.

1 Two stop bit.

Table continues on the next page...

Chapter 39 Universal Asynchronous Receiver/Transmitter (UART0)

KL25 Sub-Family Reference Manual, Rev. 3, September 2012

Freescale Semiconductor, Inc. 725

Loading...

Loading...