NOTE

For the USB FS OTG controller to operate, the minimum

system clock frequency is 20 MHz.

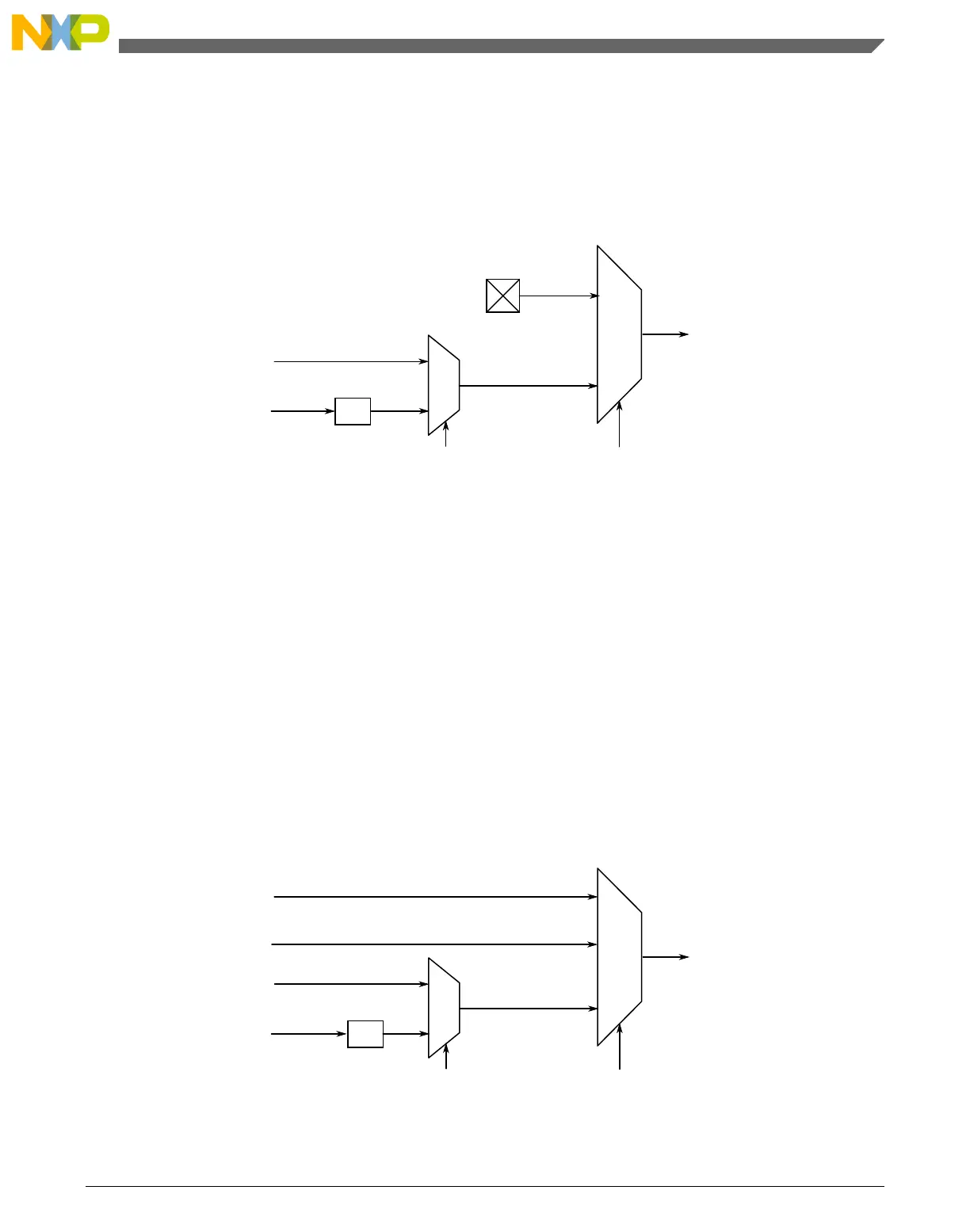

The USB OTG controller also requires a 48 MHz clock. The clock source options are

shown below.

USB 48MHz

USB_CLKIN

MCGPLLCLK

SIM_SOPT2[USBSRC]

SIM_SOPT2[PLLFLLSEL]

MCGFLLCLK

÷2

Figure 5-6. USB 48 MHz clock source

NOTE

The MCGFLLCLK does not meet the USB jitter specifications

for certification.

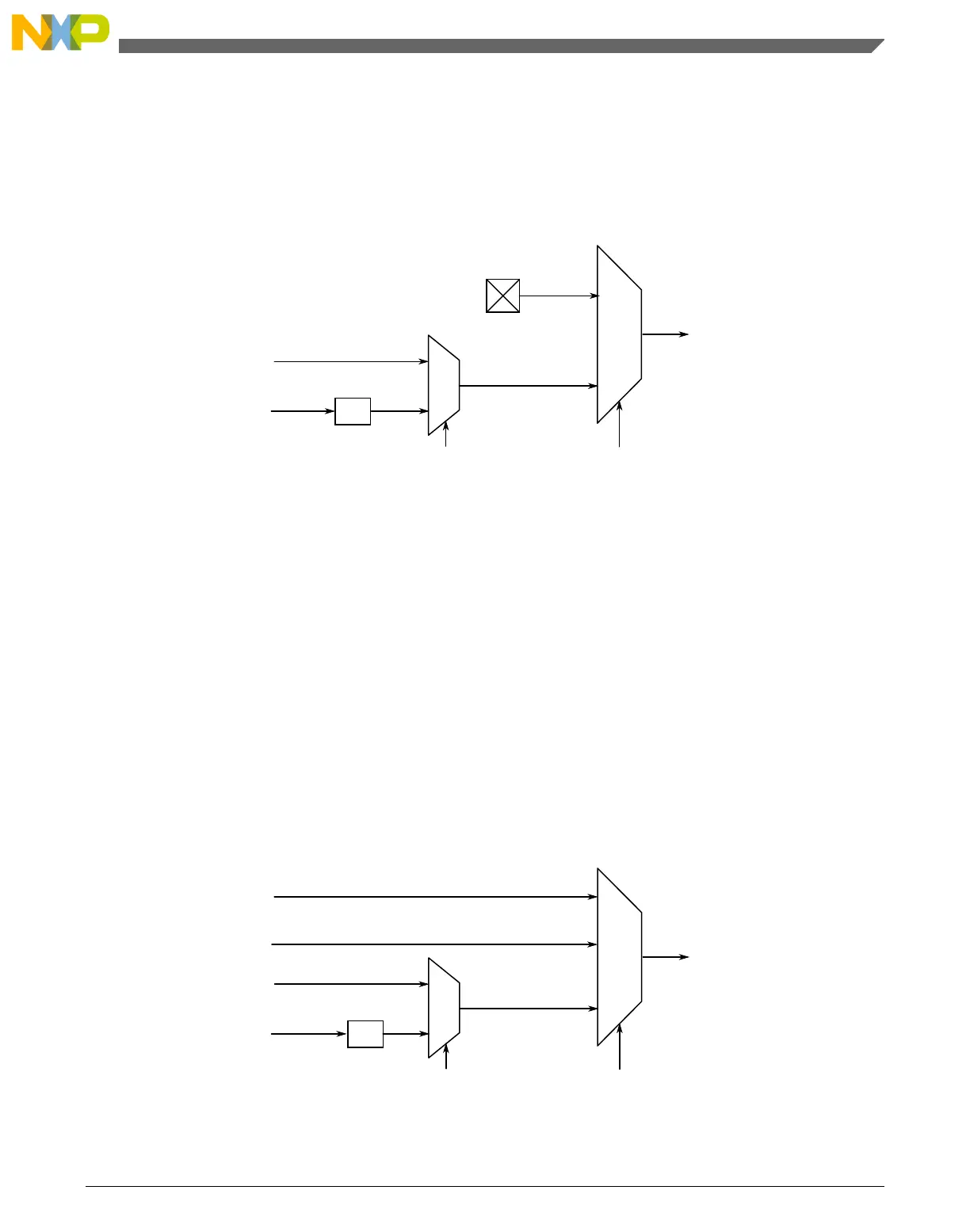

5.7.7 UART clocking

The UART0 module has a selectable clock as shown in the following figure. UART1 and

UART2 modules operate from the bus clock.

NOTE

The chosen clock must remain enabled if the UART0 is to

continue operating in all required low-power modes.

UART0 clock

MCGPLLCLK

÷2

SIM_SOPT2[UART0SRC]

SIM_SOPT2[PLLFLLSEL]

MCGFLLCLK

MCGIRCLK

OSCERCLK

Figure 5-7. UART0 clock generation

Chapter 5 Clock Distribution

KL25 Sub-Family Reference Manual, Rev. 3, September 2012

Freescale Semiconductor, Inc. 125

Loading...

Loading...