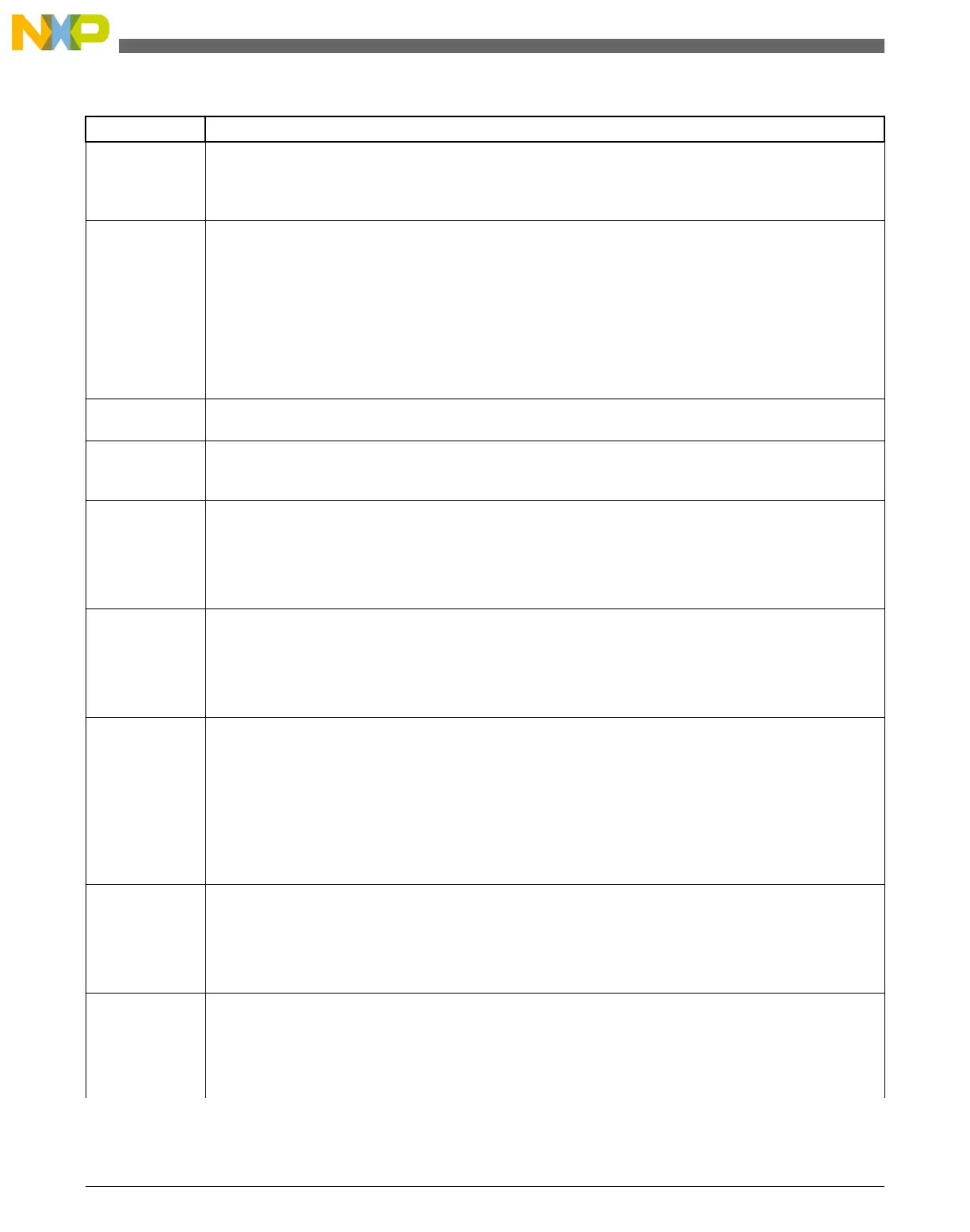

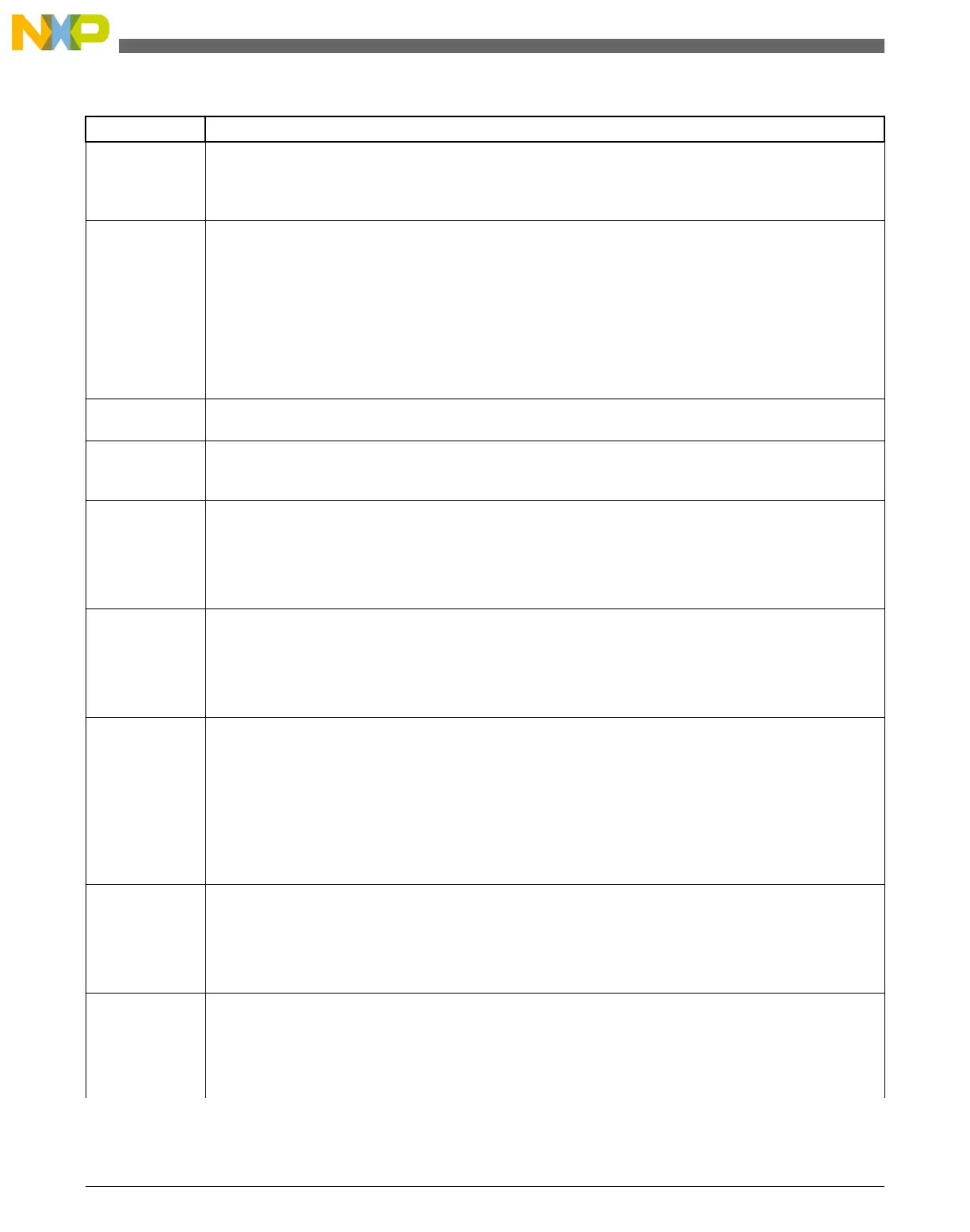

DMA_DCRn field descriptions (continued)

Field Description

29

CS

Cycle steal

0 DMA continuously makes read/write transfers until the BCR decrements to 0.

1 Forces a single read/write transfer per request.

28

AA

Auto-align

AA and SIZE bits determine whether the source or destination is auto-aligned; that is, transfers are

optimized based on the address and size.

0 Auto-align disabled

1 If SSIZE indicates a transfer no smaller than DSIZE, source accesses are auto-aligned; otherwise,

destination accesses are auto-aligned. Source alignment takes precedence over destination

alignment. If auto-alignment is enabled, the appropriate address register increments, regardless of

DINC or SINC.

27–25

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

24

Reserved

This field is reserved.

CAUTION: Must be written as zero; otherwise, undefined behavior results.

23

EADREQ

Enable asynchronous DMA requests

Enables the channel to support asynchronous DREQs while the MCU is in Stop mode.

0 Disabled

1 Enabled

22

SINC

Source increment

Controls whether the source address increments after each successful transfer.

0 No change to SAR after a successful transfer.

1 The SAR increments by 1, 2, 4 as determined by the transfer size.

21–20

SSIZE

Source size

Determines the data size of the source bus cycle for the DMA controller.

00 32-bit

01 8-bit

10 16-bit

11 Reserved (generates a configuration error (DSRn[CE]) if incorrectly specified at time of channel

activation)

19

DINC

Destination increment

Controls whether the destination address increments after each successful transfer.

0 No change to the DAR after a successful transfer.

1 The DAR increments by 1, 2, 4 depending upon the size of the transfer.

18–17

DSIZE

Destination size

Determines the data size of the destination bus cycle for the DMA controller.

00 32-bit

01 8-bit

Table continues on the next page...

Memory Map and Registers

KL25 Sub-Family Reference Manual, Rev. 3, September 2012

358 Freescale Semiconductor, Inc.

Loading...

Loading...