MCG_SC field descriptions (continued)

Field Description

3–1

FCRDIV

Fast Clock Internal Reference Divider

Selects the amount to divide down the fast internal reference clock. The resulting frequency will be in the

range 31.25 kHz to 4 MHz (Note: Changing the divider when the Fast IRC is enabled is not supported).

000 Divide Factor is 1

001 Divide Factor is 2.

010 Divide Factor is 4.

011 Divide Factor is 8.

100 Divide Factor is 16

101 Divide Factor is 32

110 Divide Factor is 64

111 Divide Factor is 128.

0

LOCS0

OSC0 Loss of Clock Status

The LOCS0 indicates when a loss of OSC0 reference clock has occurred. The LOCS0 bit only has an

effect when CME0 is set. This bit is cleared by writing a logic 1 to it when set.

0 Loss of OSC0 has not occurred.

1 Loss of OSC0 has occurred.

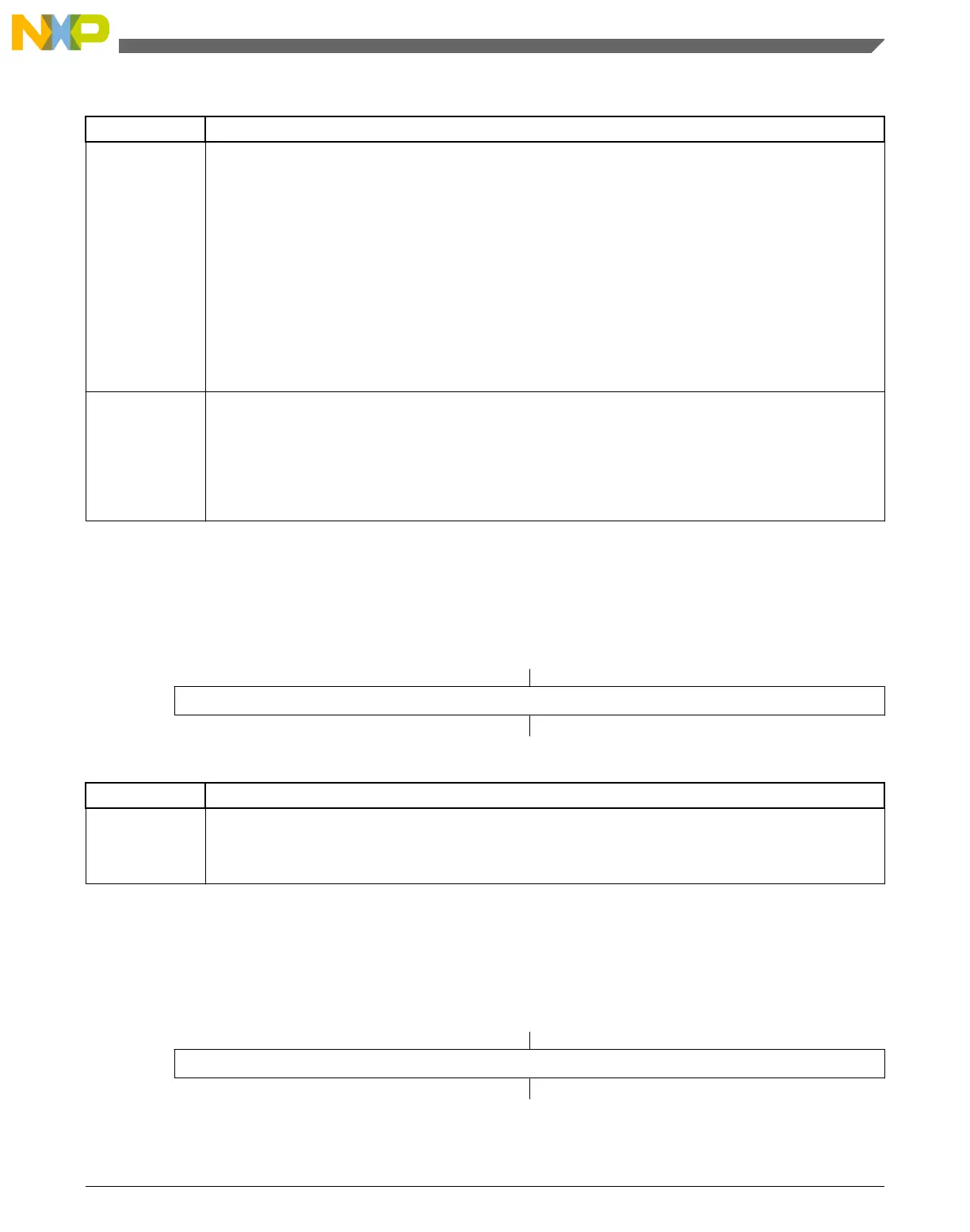

24.3.9 MCG Auto Trim Compare Value High Register (MCG_ATCVH)

Address: 4006_4000h base + Ah offset = 4006_400Ah

Bit 7 6 5 4 3 2 1 0

Read

ATCVH

Write

Reset

0 0 0 0 0 0 0 0

MCG_ATCVH field descriptions

Field Description

7–0

ATCVH

ATM Compare Value High

Values are used by Auto Trim Machine to compare and adjust Internal Reference trim values during ATM

SAR conversion.

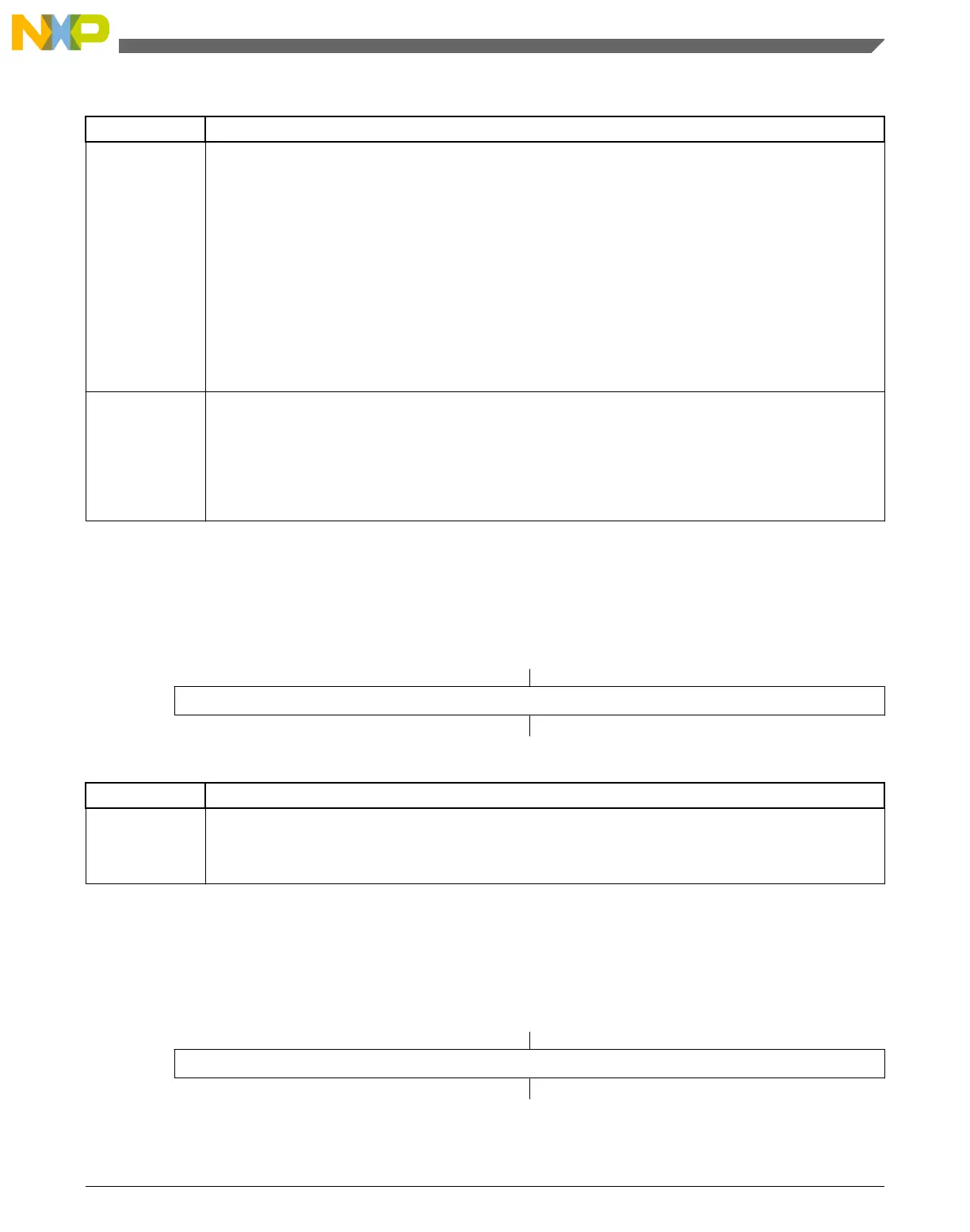

24.3.10 MCG Auto Trim Compare Value Low Register (MCG_ATCVL)

Address: 4006_4000h base + Bh offset = 4006_400Bh

Bit 7 6 5 4 3 2 1 0

Read

ATCVL

Write

Reset

0 0 0 0 0 0 0 0

Chapter 24 Multipurpose Clock Generator (MCG)

KL25 Sub-Family Reference Manual, Rev. 3, September 2012

Freescale Semiconductor, Inc. 381

Loading...

Loading...