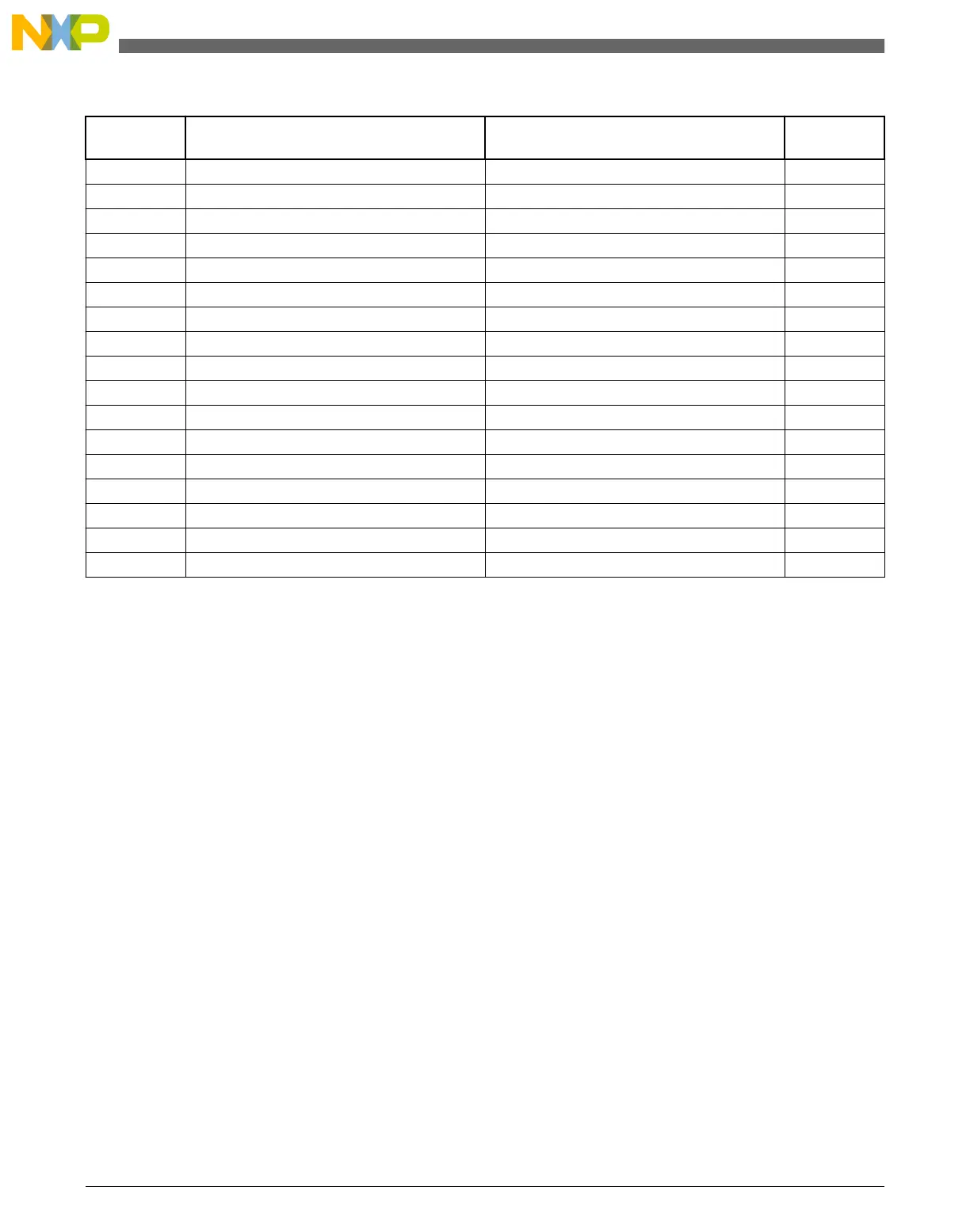

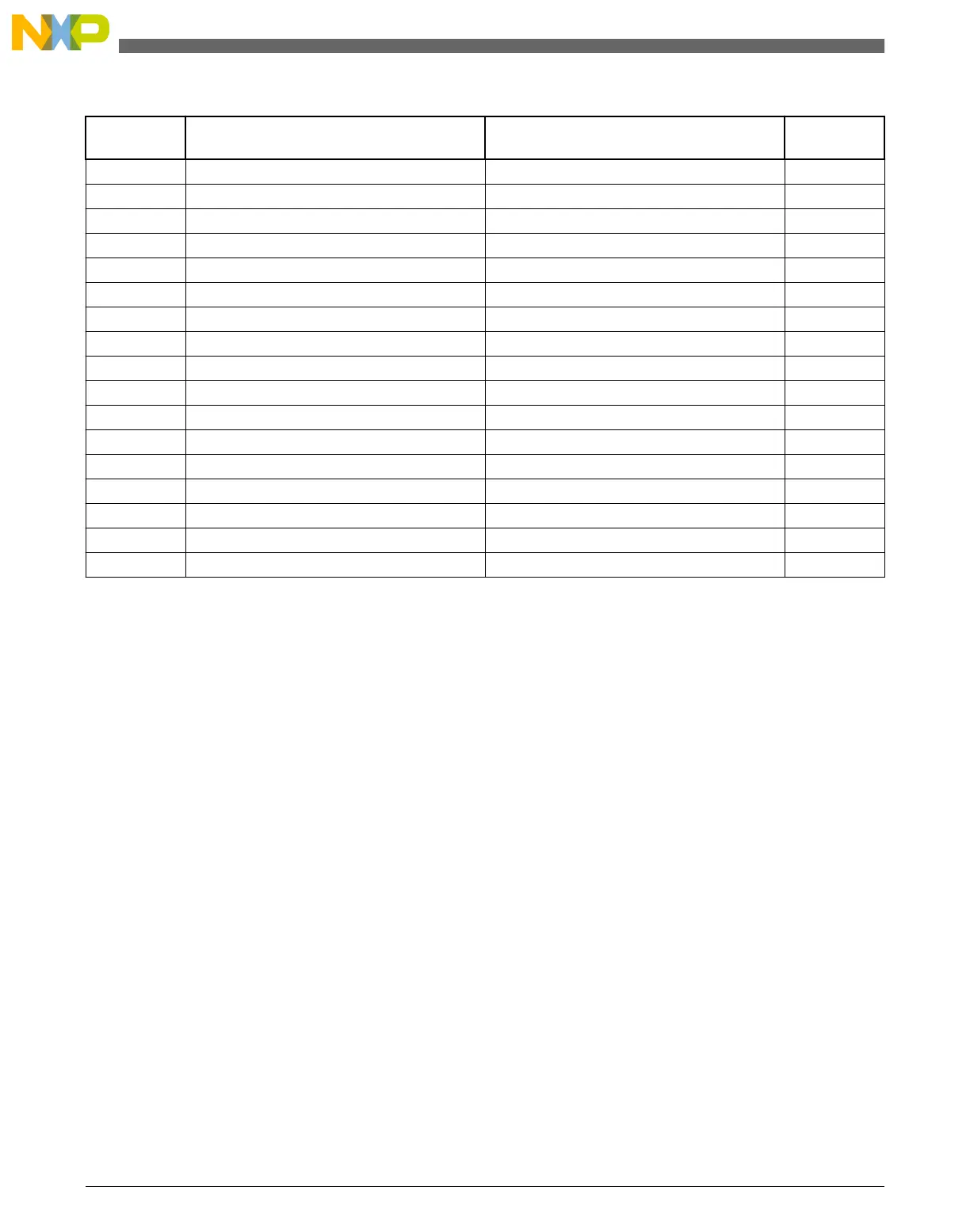

Table 3-20. DMA request sources - MUX 0 (continued)

Source

number

Source module Source description Async DMA

capable

47 Reserved —

48 Reserved —

49 Port control module Port A Yes

50 Reserved —

51 Reserved —

52 Port control module Port D Yes

53 Reserved —

54 TPM0 Overflow Yes

55 TPM1 Overflow Yes

56 TPM2 Overflow Yes

57 TSI — Yes

58 Reserved —

59 Reserved —

60 DMA MUX Always enabled

61 DMA MUX Always enabled

62 DMA MUX Always enabled

63 DMA MUX Always enabled

1. Configuring a DMA channel to select source 0 or any of the reserved sources disables that DMA channel.

3.4.8.2 DMA transfers via PIT trigger

The PIT module can trigger a DMA transfer on the first two DMA channels. The

assignments are detailed at PIT/DMA Periodic Trigger Assignments .

3.4.9 DMA Controller Configuration

This section summarizes how the module has been configured in the chip. For a

comprehensive description of the module itself, see the module’s dedicated chapter.

System Modules

KL25 Sub-Family Reference Manual, Rev. 3, September 2012

66 Freescale Semiconductor, Inc.

Loading...

Loading...