33.4.6 LPTMR hardware trigger

The LPTMR hardware trigger asserts at the same time the CSR[TCF] is set and can be

used to trigger hardware events in other peripherals without software intervention. The

hardware trigger is always enabled.

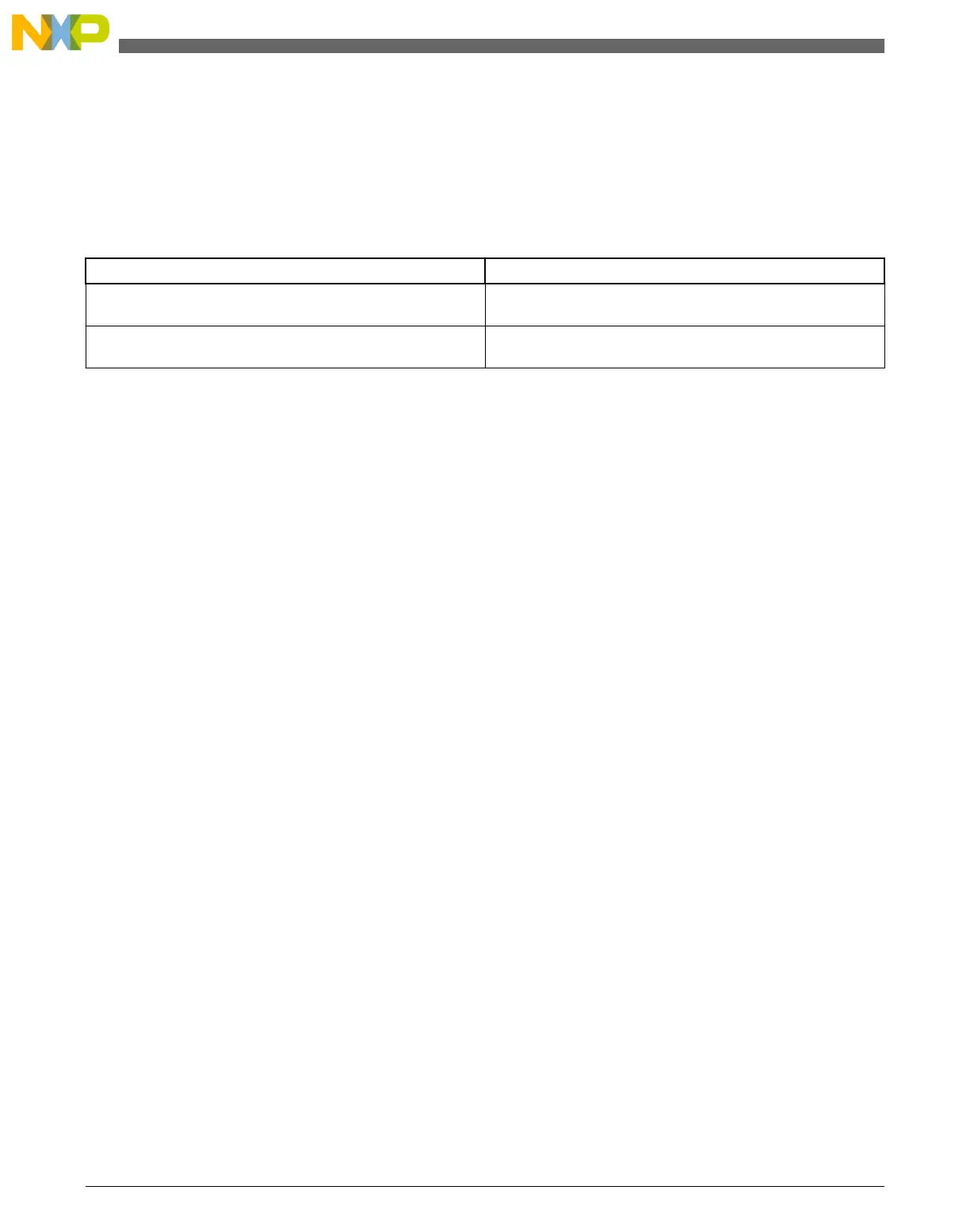

When Then

The CMR is set to 0 with CSR[TFC] clear The LPTMR hardware trigger will assert on the first compare

and does not deassert.

The CMR is set to a nonzero value, or, if CSR[TFC] is set The LPTMR hardware trigger will assert on each compare

and deassert on the following increment of the CNR.

33.4.7 LPTMR interrupt

The LPTMR interrupt is generated whenever CSR[TIE] and CSR[TCF] are set.

CSR[TCF] is cleared by disabling the LPTMR or by writing a logic 1 to it.

CSR[TIE] can be altered and CSR[TCF] can be cleared while the LPTMR is enabled.

The LPTMR interrupt is generated asynchronously to the system clock and can be used to

generate a wakeup from any low-power mode, including the low-leakage modes,

provided the LPTMR is enabled as a wakeup source.

Functional description

KL25 Sub-Family Reference Manual, Rev. 3, September 2012

596 Freescale Semiconductor, Inc.

Loading...

Loading...