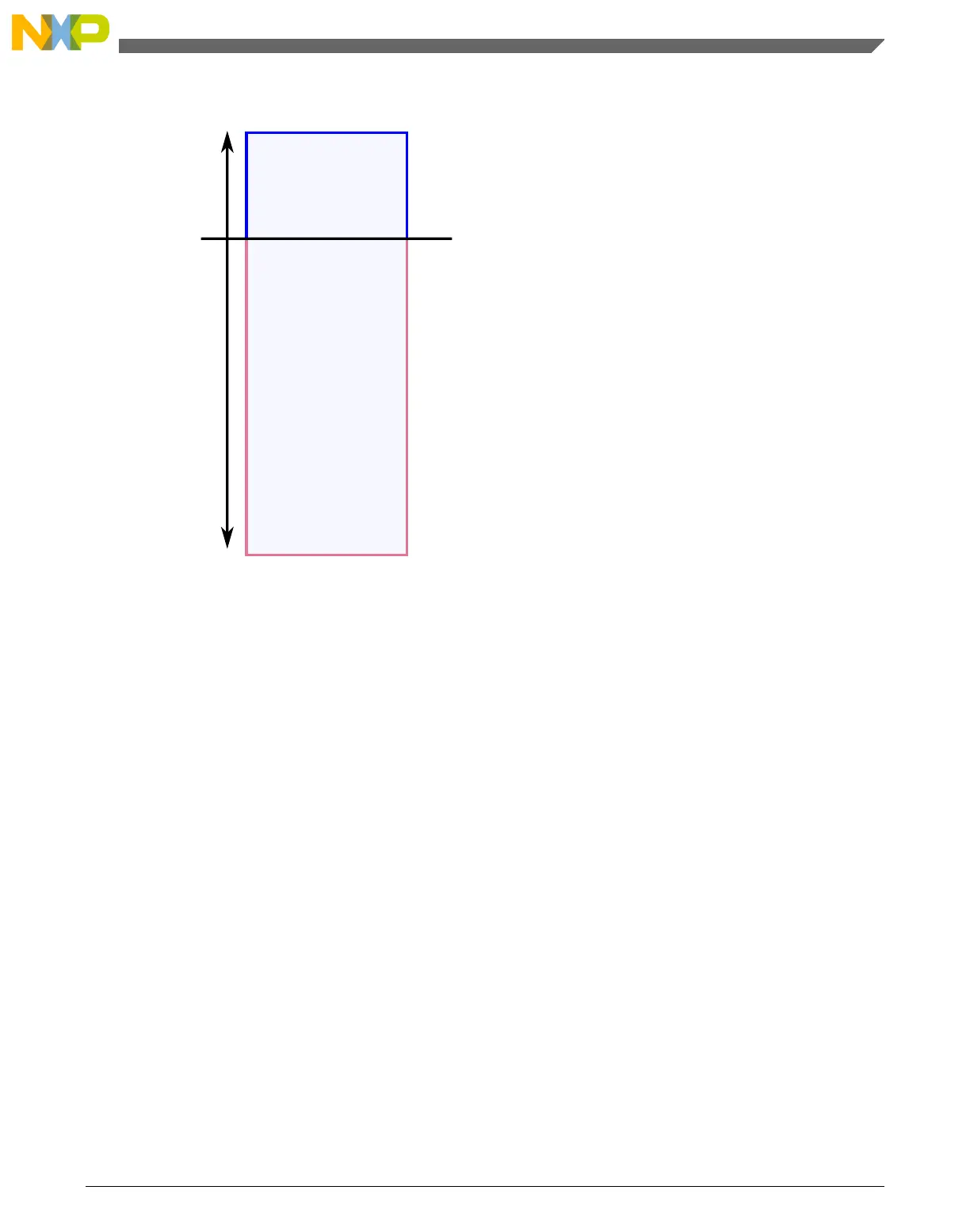

SRAM_U

0x2000_0000

SRAM size *(1/4)

SRAM_L

0x1FFF_FFFF

SRAM size * (3/4)

0x2000_0000 – SRAM_size/4

0x2000_0000 + SRAM_size(3/4) - 1

Figure 3-20. SRAM blocks memory map

For example, for a device containing 16 KB of SRAM the ranges are:

• SRAM_L: 0x1FFF_F000 – 0x1FFF_FFFF

• SRAM_U: 0x2000_0000 – 0x2000_2FFF

3.6.3.3 SRAM retention in low power modes

The SRAM is retained down to VLLS3 mode. In VLLS1 and VLLS0 no SRAM is

retained.

Analog

3.7.1 16-bit SAR ADC Configuration

This section summarizes how the module has been configured in the chip. For a

comprehensive description of the module itself, see the module’s dedicated chapter.

3.7

Chapter 3 Chip Configuration

KL25 Sub-Family Reference Manual, Rev. 3, September 2012

Freescale Semiconductor, Inc. 77

Loading...

Loading...