• Channels which implement the normal routing functionality plus periodic triggering

capability

• Channels which implement only the normal routing functionality

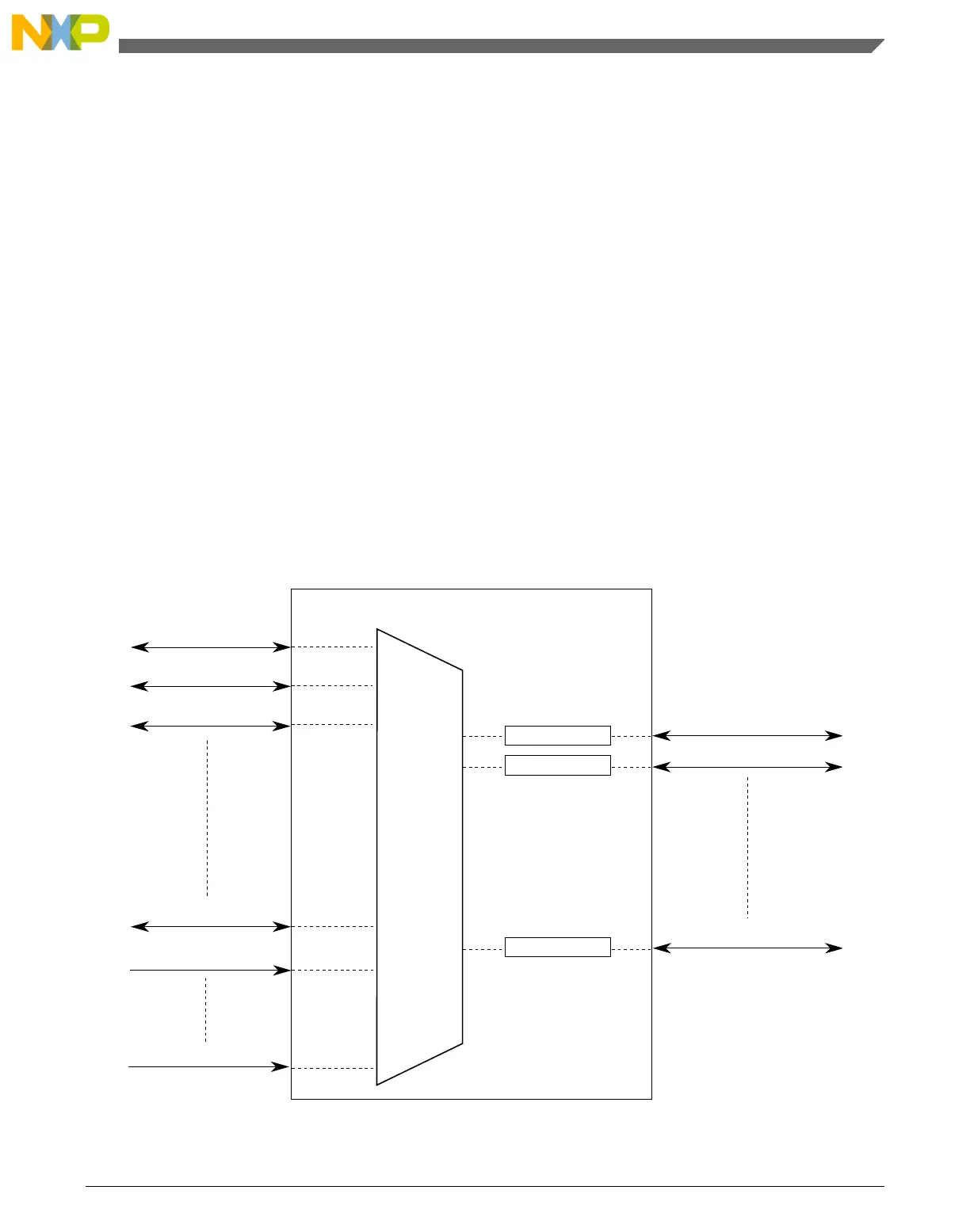

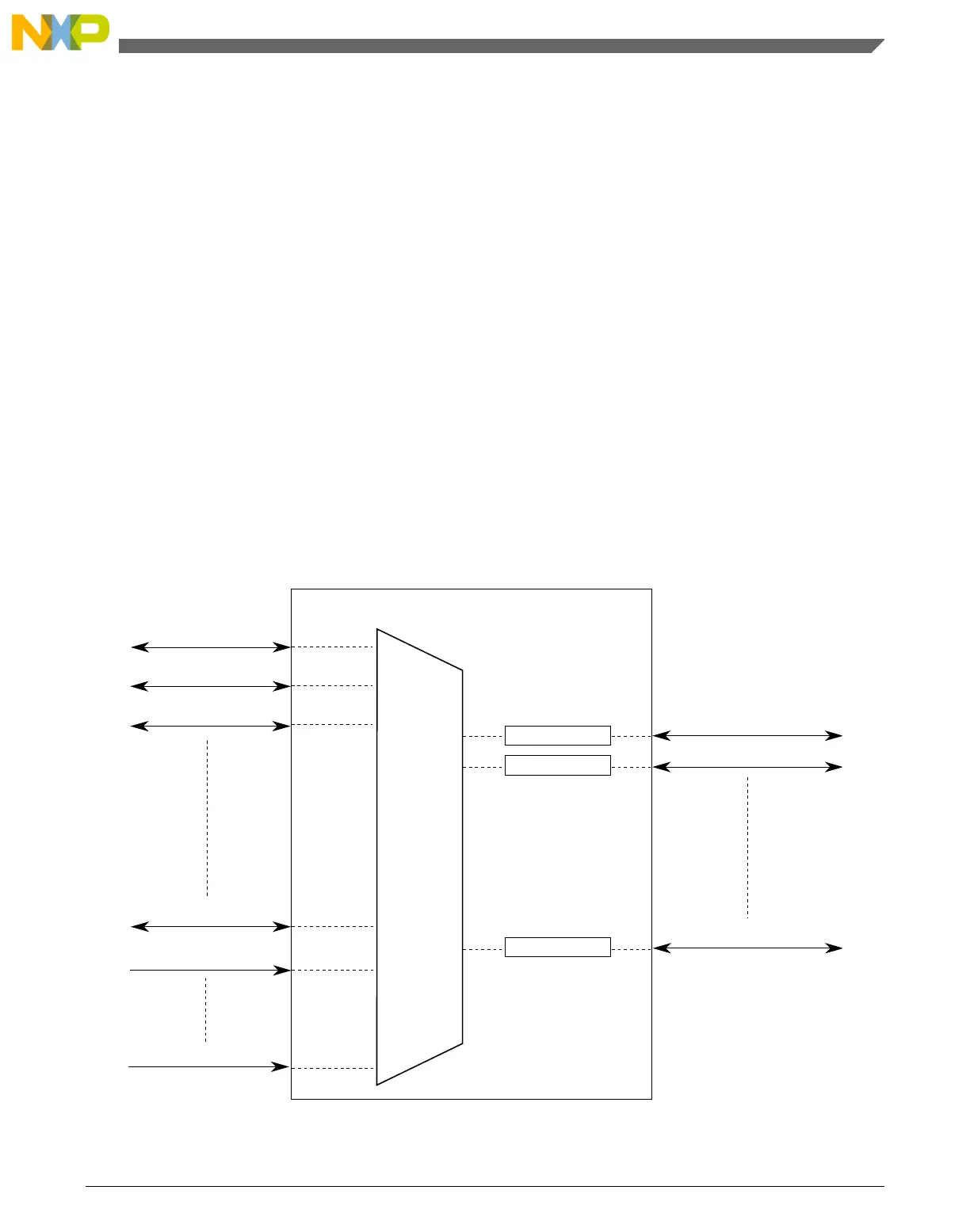

22.4.1 DMA channels with periodic triggering capability

Besides the normal routing functionality, the first 2 channels of the DMAMUX provide a

special periodic triggering capability that can be used to provide an automatic mechanism

to transmit bytes, frames, or packets at fixed intervals without the need for processor

intervention. The trigger is generated by the periodic interrupt timer (PIT); as such, the

configuration of the periodic triggering interval is done via configuration registers in the

PIT. See the section on periodic interrupt timer for more information on this topic.

Note

Because of the dynamic nature of the system (due to DMA

channel priorities, bus arbitration, interrupt service routine

lengths, etc.), the number of clock cycles between a trigger and

the actual DMA transfer cannot be guaranteed.

DMA channel #0

Trigger #2

Source #1

Source #2

Source #3

Always #1

DMA channel #3

Always #y

Trigger #4

Source #x

Trigger #1

DMA channel #1

Figure 22-12. DMAMUX triggered channels

Chapter 22 Direct Memory Access Multiplexer (DMAMUX)

KL25 Sub-Family Reference Manual, Rev. 3, September 2012

Freescale Semiconductor, Inc. 341

Loading...

Loading...