NOTE

Setting multiple CHCFG registers with the same Source value

will result in unpredictable behavior.

NOTE

Before changing the trigger or source settings a DMA channel

must be disabled via the CHCFGn[ENBL] bit.

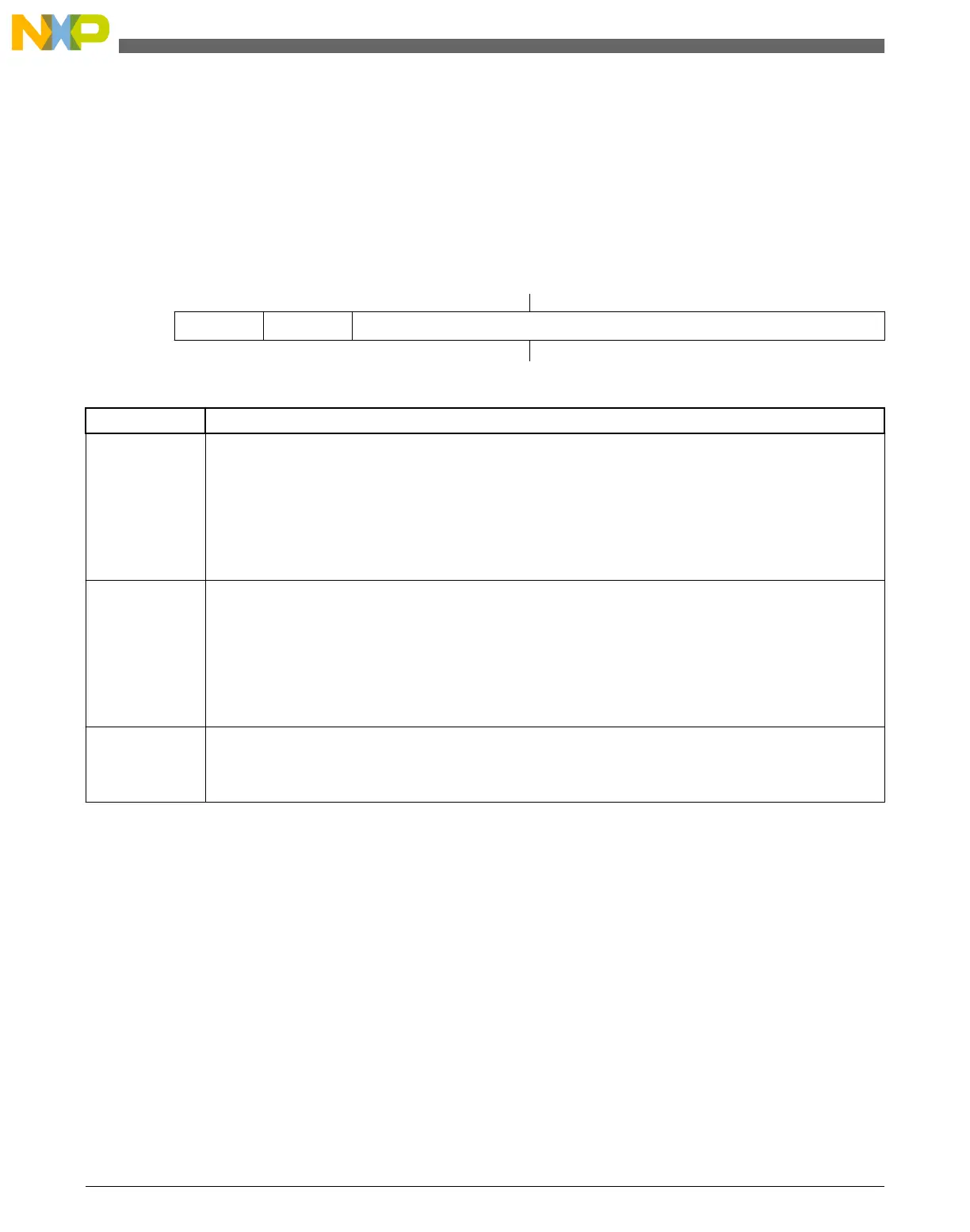

Address: 4002_1000h base + 0h offset + (1d × i), where i=0d to 3d

Bit 7 6 5 4 3 2 1 0

Read

ENBL TRIG SOURCE

Write

Reset

0 0 0 0 0 0 0 0

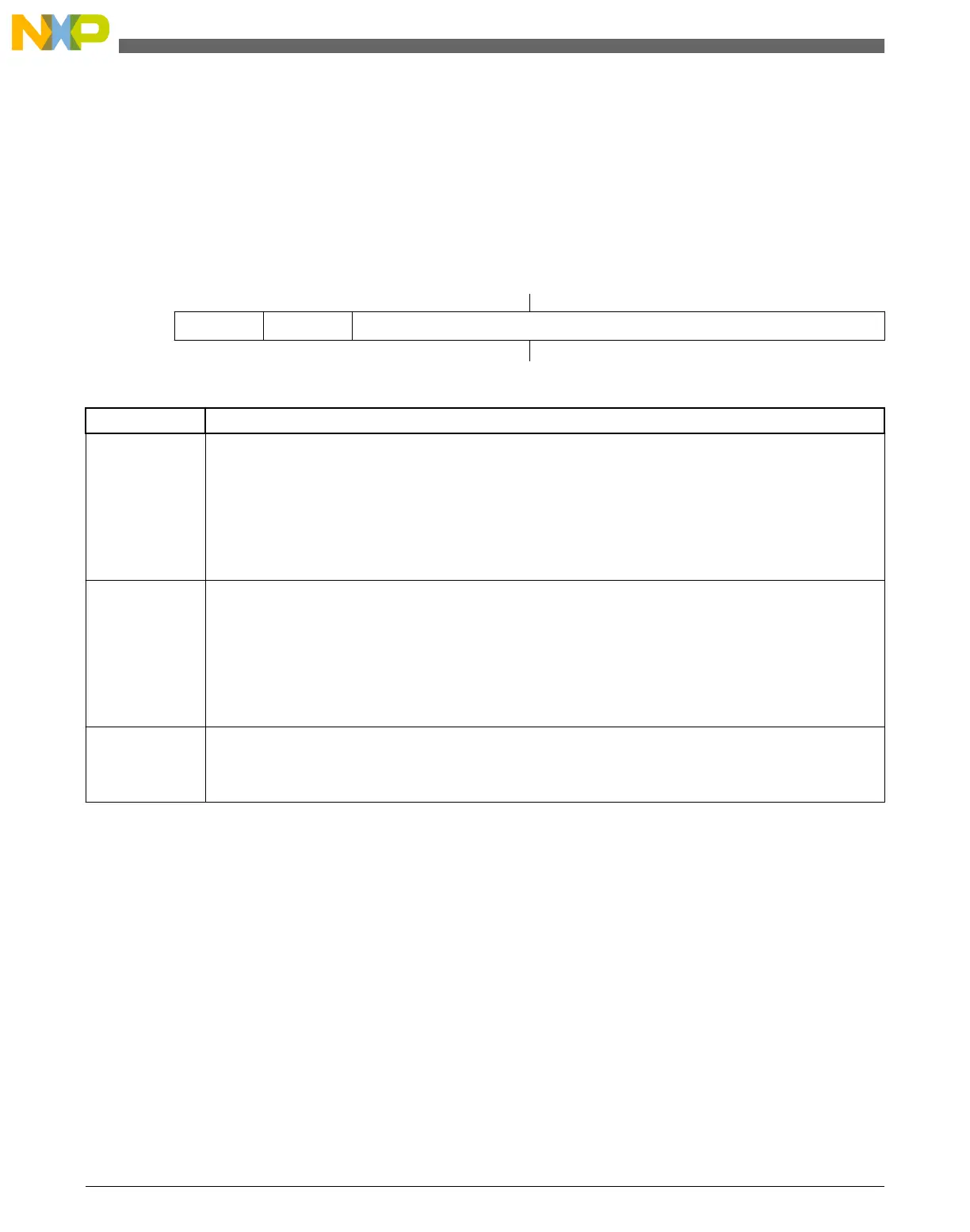

DMAMUXx_CHCFGn field descriptions

Field Description

7

ENBL

DMA Channel Enable

Enables the DMA channel.

0 DMA channel is disabled. This mode is primarily used during configuration of the DMA Mux. The DMA

has separate channel enables/disables, which should be used to disable or re-configure a DMA

channel.

1 DMA channel is enabled

6

TRIG

DMA Channel Trigger Enable

Enables the periodic trigger capability for the triggered DMA channel.

0 Triggering is disabled. If triggering is disabled, and the ENBL bit is set, the DMA Channel will simply

route the specified source to the DMA channel. (Normal mode)

1 Triggering is enabled. If triggering is enabled, and the ENBL bit is set, the DMAMUX is in Periodic

Trigger mode.

5–0

SOURCE

DMA Channel Source (Slot)

Specifies which DMA source, if any, is routed to a particular DMA channel. See your device's chip

configuration details for further details about the peripherals and their slot numbers.

22.4 Functional description

The primary purpose of the DMAMUX is to provide flexibility in the system's use of the

available DMA channels. As such, configuration of the DMAMUX is intended to be a

static procedure done during execution of the system boot code. However, if the

procedure outlined in Enabling and configuring sources is followed, the configuration of

the DMAMUX may be changed during the normal operation of the system.

Functionally, the DMAMUX channels may be divided into two classes:

Functional description

KL25 Sub-Family Reference Manual, Rev. 3, September 2012

340 Freescale Semiconductor, Inc.

Loading...

Loading...