3.4.10.3 Clock Gating

This family of devices includes clock gating control for each peripheral, that is, the clock

to each peripheral can explicitly be gated on or off, using clock-gate control bits in the

SIM module.

Clock Modules

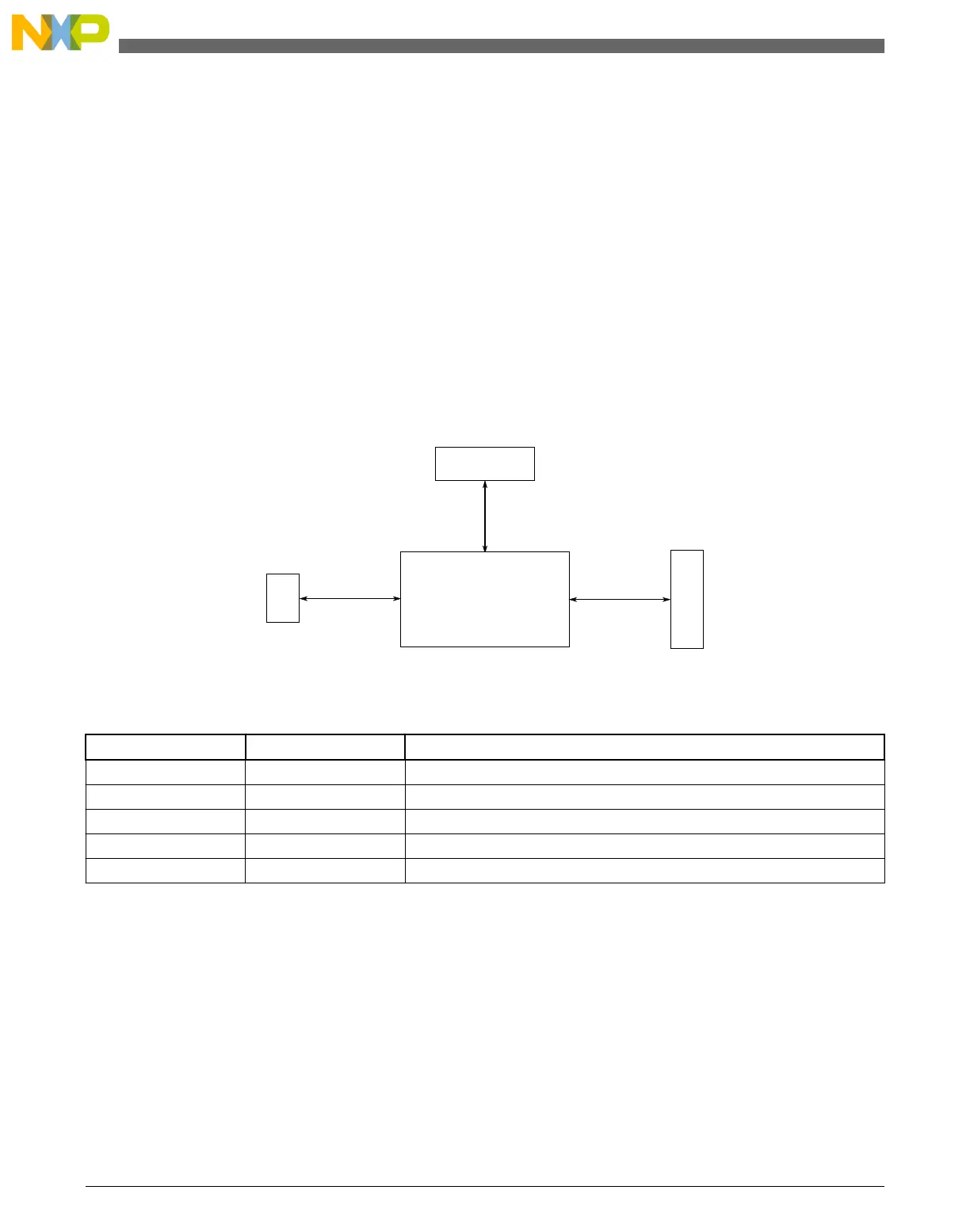

3.5.1 MCG Configuration

This section summarizes how the module has been configured in the chip. For a

comprehensive description of the module itself, see the module’s dedicated chapter.

Register

access

Peripheral

bridge

Multipurpose Clock

Generator (MCG)

System

oscillator

System integration

module (SIM)

Figure 3-14. MCG configuration

Table 3-24. Reference links to related information

Topic Related module Reference

Full description MCG MCG

System memory map System memory map

Clocking Clock distribution

Power management Power management

Signal multiplexing Port control Signal multiplexing

3.5.1.1 MCG FLL modes

On L-series devices the MCGFLLCLK frequency is limited to 48 MHz max. The DCO is

limited to the two lowest range settings (MCG_C4[DRST_DRS] must be set to either

0b00 or 0b01).

3.5

Clock Modules

KL25 Sub-Family Reference Manual, Rev. 3, September 2012

70 Freescale Semiconductor, Inc.

Loading...

Loading...