Reading the CNT register adds two wait states to the register access due to

synchronization delays.

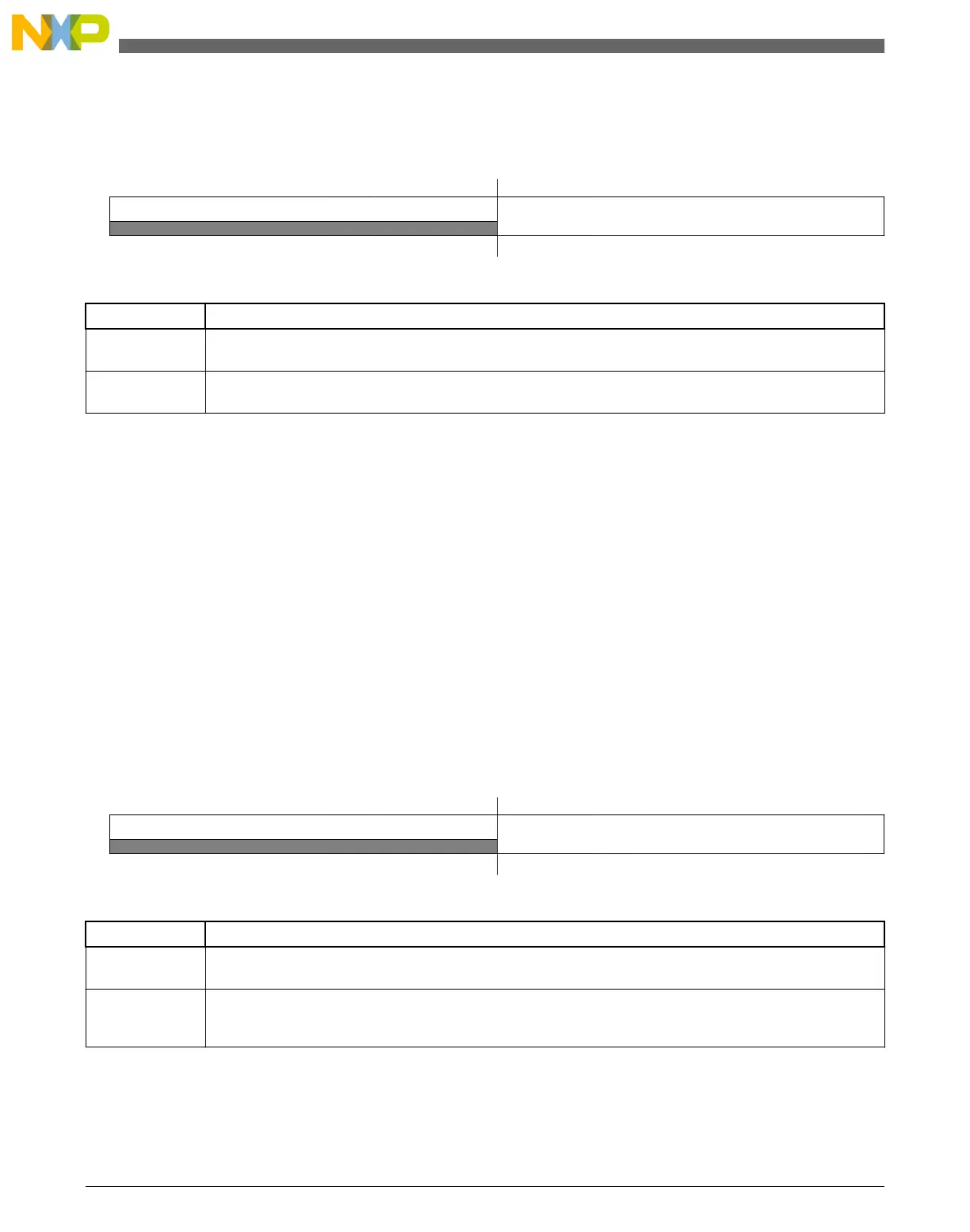

Address: Base address + 4h offset

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

R

0

COUNT

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

TPMx_CNT field descriptions

Field Description

31–16

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

15–0

COUNT

Counter value

31.3.3 Modulo (TPMx_MOD)

The Modulo register contains the modulo value for the LPTPM counter. When the

LPTPM counter reaches the modulo value and increments, the overflow flag (TOF) is set

and the next value of LPTPM counter depends on the selected counting method (see

Counter ).

Writing to the MOD register latches the value into a buffer. The MOD register is updated

with the value of its write buffer according to MOD Register Update .

It is recommended to initialize the LPTPM counter (write to CNT) before writing to the

MOD register to avoid confusion about when the first counter overflow will occur.

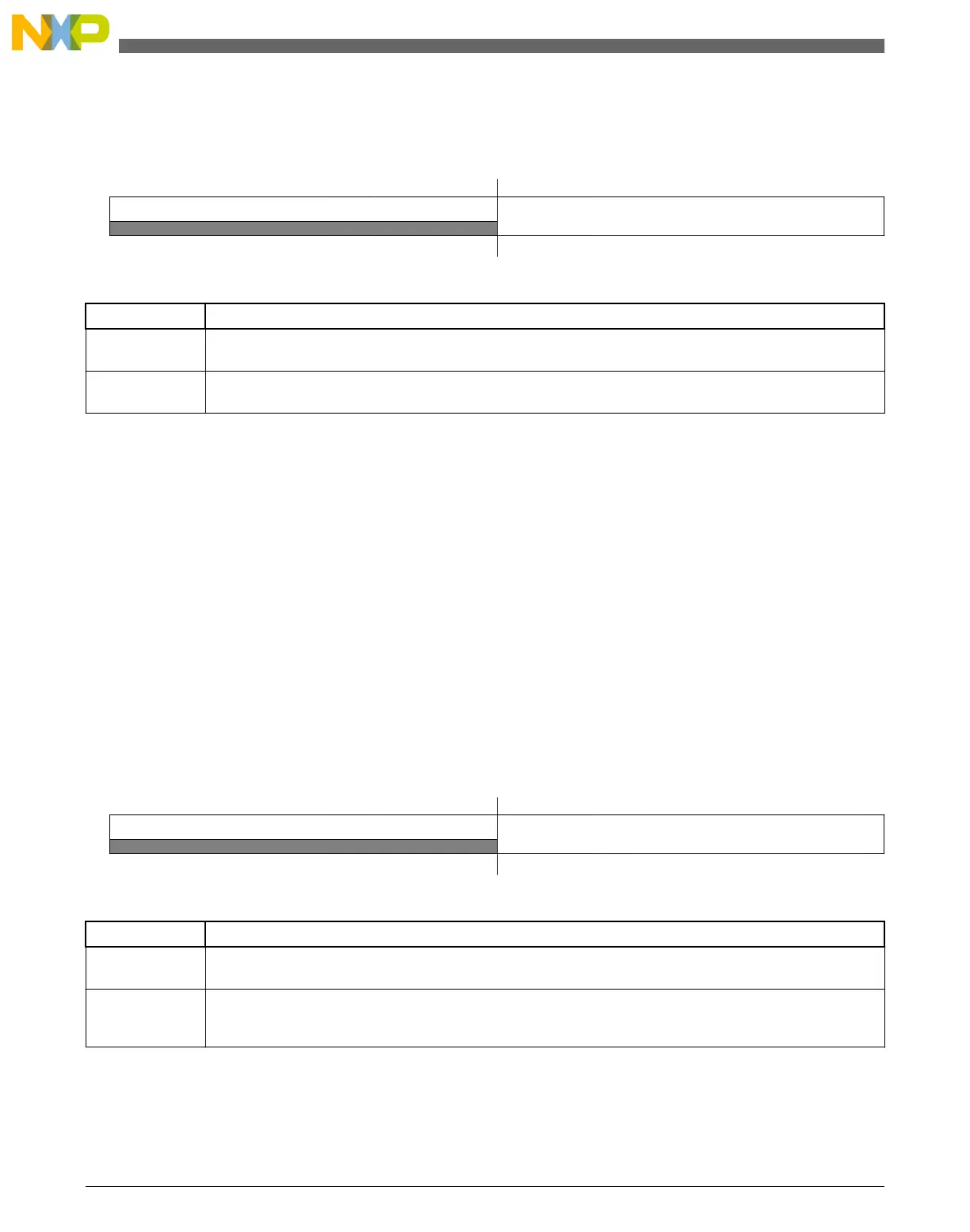

Address: Base address + 8h offset

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

R

0

MOD

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

TPMx_MOD field descriptions

Field Description

31–16

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

15–0

MOD

Modulo value

When writing this field, all bytes must be written at the same time.

Memory Map and Register Definition

KL25 Sub-Family Reference Manual, Rev. 3, September 2012

554 Freescale Semiconductor, Inc.

Loading...

Loading...