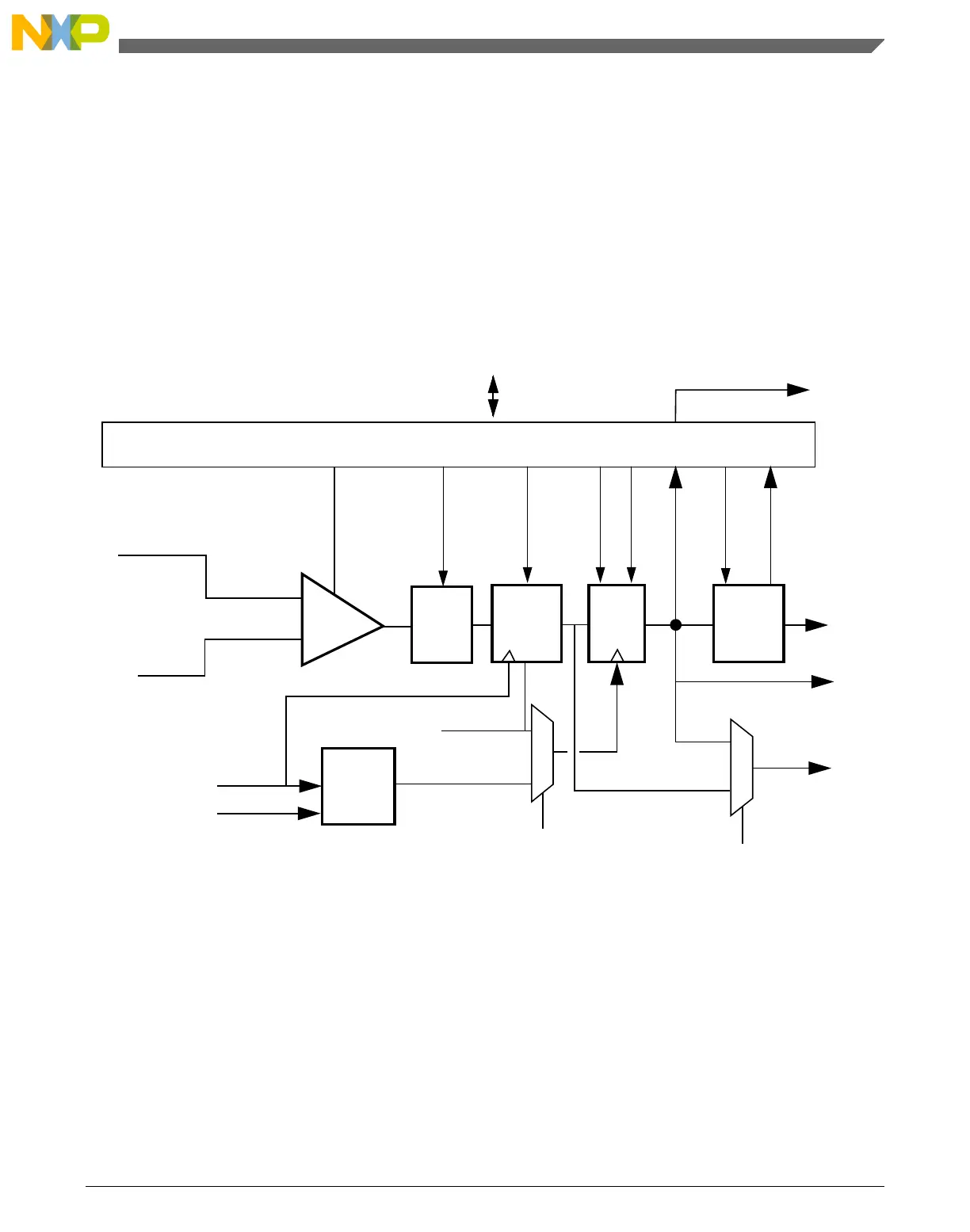

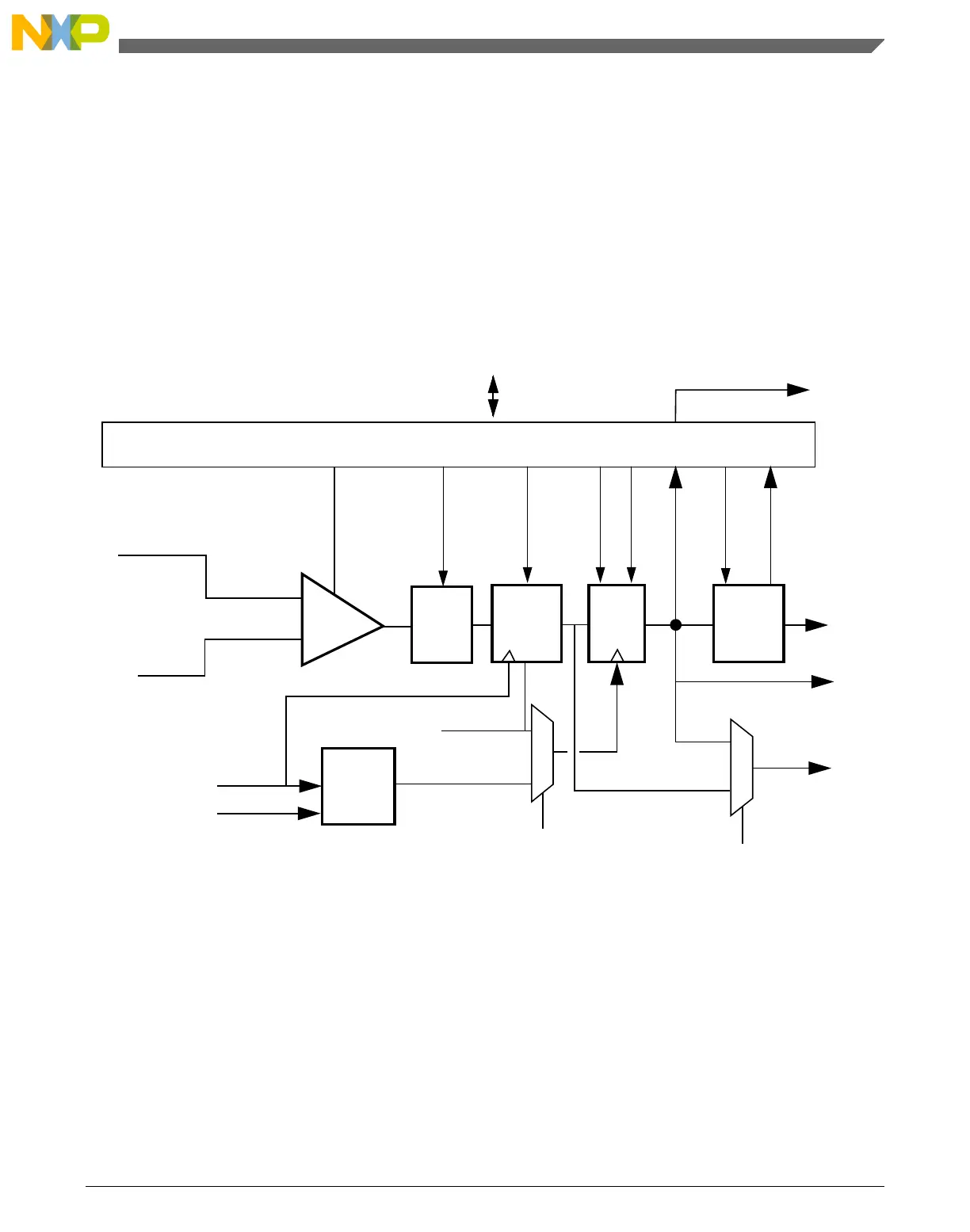

29.8.1.7 Windowed/Filtered mode (#7)

This is the most complex mode of operation for the comparator block, as it uses both

windowing and filtering features. It also has the highest latency of any of the modes. This

can be approximated: up to 1 bus clock synchronization in the window function +

((CR0[FILTER_CNT] * FPR[FILT_PER]) + 1) * bus clock for the filter function.

When any windowed mode is active, COUTA is clocked by the bus clock whenever

WINDOW = 1. The last latched value is held when WINDOW = 0.

+

-

IRQ

EN, PMODE,HYSCTR[1:0]

INP

INM

FILTER_CNT

INV

COUT

COUT

OPE

SE

CMPO to

PAD

COUTA

0

1

WE

1

0

SE=0

CGMUX

COS

FILT_PER

01

+

-

FILT_PER

bus clock

COS

>

IER/F CFR/F

WINDOW/SAMPLE

Polarity

select

Window

control

Filter

block

Interrupt

control

divided

bus

clock

Clock

prescaler

CMPO

0x01

To other SOC functions

Internal bus

Figure 29-23. Windowed/Filtered mode

29.8.2 Power modes

29.8.2.1 Wait mode operation

During Wait and VLPW modes, the CMP, if enabled, continues to operate normally and

a CMP interrupt can wake the MCU.

Chapter 29 Comparator (CMP)

KL25 Sub-Family Reference Manual, Rev. 3, September 2012

Freescale Semiconductor, Inc. 529

Loading...

Loading...