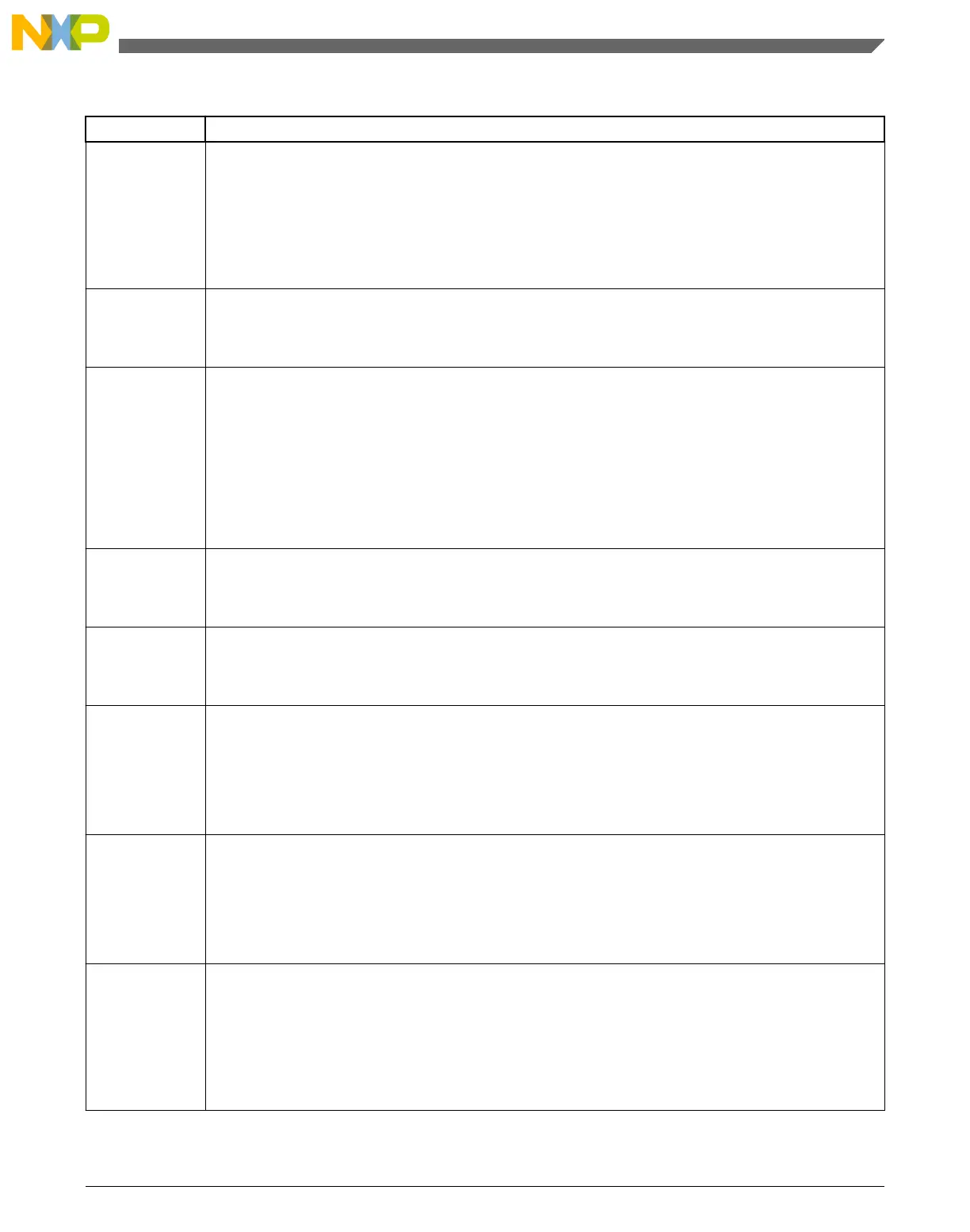

UARTx_C1 field descriptions

Field Description

7

LOOPS

Loop Mode Select

Selects between loop back modes and normal 2-pin full-duplex modes. When LOOPS is set, the

transmitter output is internally connected to the receiver input.

0 Normal operation - UART _RX and UART _TX use separate pins.

1 Loop mode or single-wire mode where transmitter outputs are internally connected to receiver input.

(See RSRC bit.) UART _RX pin is not used by UART .

6

DOZEEN

Doze Enable

0 UART is enabled in Wait mode.

1 UART is disabled in Wait mode.

5

RSRC

Receiver Source Select

This bit has no meaning or effect unless the LOOPS bit is set to 1. When LOOPS is set, the receiver input

is internally connected to the UART _TX pin and RSRC determines whether this connection is also

connected to the transmitter output.

0 Provided LOOPS is set, RSRC is cleared, selects internal loop back mode and the UART does not

use the UART _RX pins.

1 Single-wire UART mode where the UART _TX pin is connected to the transmitter output and receiver

input.

4

M

9-Bit or 8-Bit Mode Select

0 Receiver and transmitter use 8-bit data characters.

1 Receiver and transmitter use 9-bit data characters.

3

WAKE

Receiver Wakeup Method Select

0 Idle-line wakeup.

1 Address-mark wakeup.

2

ILT

Idle Line Type Select

Setting this bit to 1 ensures that the stop bits and logic 1 bits at the end of a character do not count toward

the 10 to 13 bit times of logic high level needed by the idle line detection logic.

0 Idle character bit count starts after start bit.

1 Idle character bit count starts after stop bit.

1

PE

Parity Enable

Enables hardware parity generation and checking. When parity is enabled, the bit immediately before the

stop bit is treated as the parity bit.

0 No hardware parity generation or checking.

1 Parity enabled.

0

PT

Parity Type

Provided parity is enabled (PE = 1), this bit selects even or odd parity. Odd parity means the total number

of 1s in the data character, including the parity bit, is odd. Even parity means the total number of 1s in the

data character, including the parity bit, is even.

0 Even parity.

1 Odd parity.

Chapter 39 Universal Asynchronous Receiver/Transmitter (UART0)

KL25 Sub-Family Reference Manual, Rev. 3, September 2012

Freescale Semiconductor, Inc. 727

Loading...

Loading...