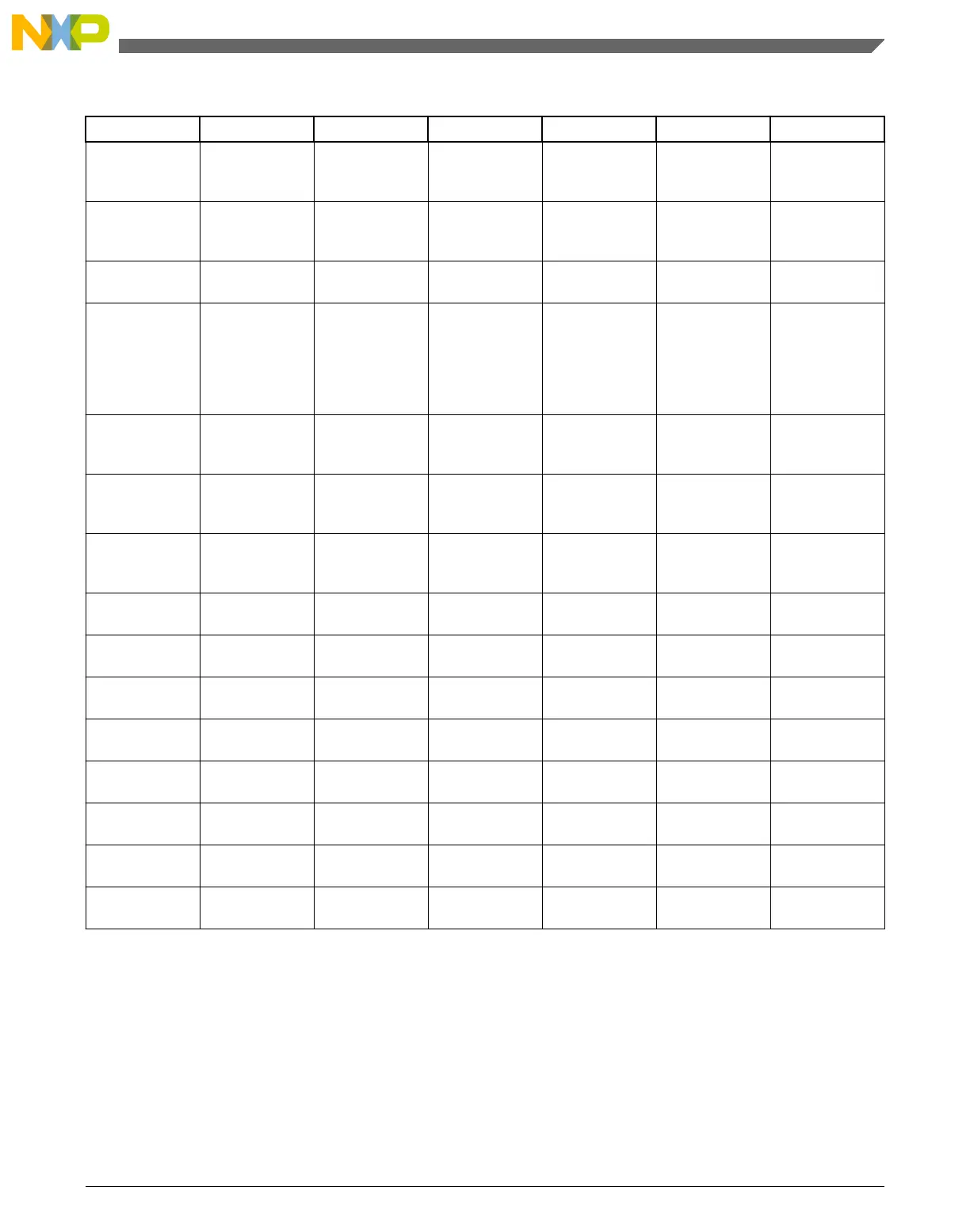

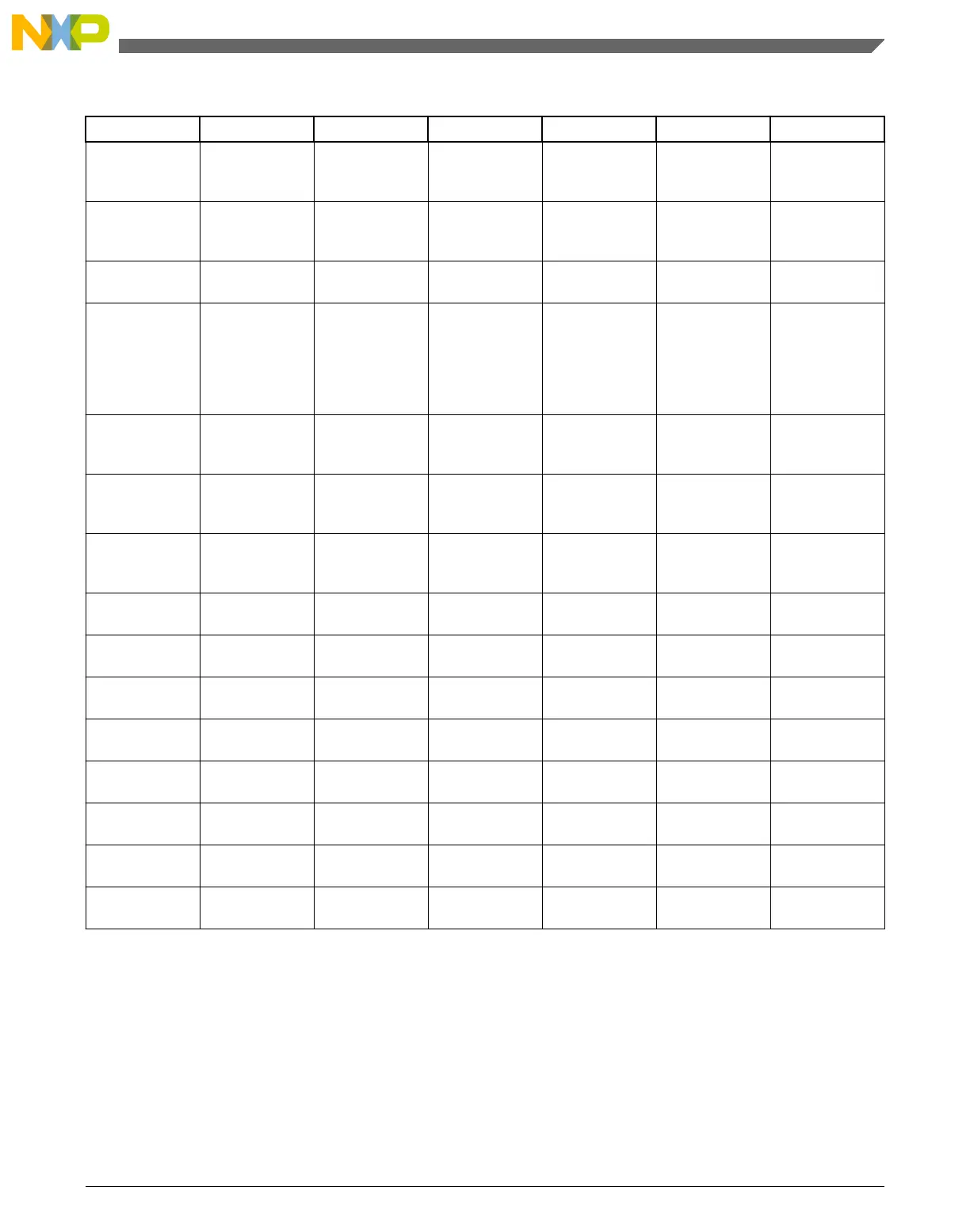

Table 3-1. Module to Module Interconnects (continued)

Peripheral Signal — to Peripheral Use Case Control Comment

LPTMR Hardware trigger to TPMx TPM Trigger

input

TPMx_CONF[T

RGSEL] (4 bit

field)

—

TPMx TOF to TPMx TPM Trigger

input

TPMx_CONF[T

RGSEL] (4 bit

field)

—

TPM1 Timebase to TPMx TPM Global

timebase input

TPMx_CONF[G

TBEEN]

—

PIT CHx TIF0, TIF1 to TPMx TPM Trigger

input

TPMx_CONF[T

RGSEL] (4 bit

field)

If PIT is

triggering the

TPM, the TPM

clock must be

faster than Bus

clock.

RTC ALARM or

SECONDS

to TPMx TPM Trigger

input

TPMx_CONF[T

RGSEL] (4 bit

field)

—

EXTRG_IN EXTRG_IN to TPMx TPM Trigger

input

TPMx_CONF[T

RGSEL] (4 bit

field)

—

CMP0 CMP0_OUT to TPMx TPM Trigger

input

TPMx_CONF[T

RGSEL] (4 bit

field)

—

LPTMR Hardware trigger to TSI TSI triggering TSI selects HW

trigger

—

UART0 UART0_TX to Modulated by

TPM1 CH0

UART

modulation

SOPT5_UART0

TXSRC

—

UART0 UART0_TX to Modulated by

TPM2 CH0

UART

modulation

SOPT5_UART0

TXSRC

—

UART1 UART1_TX to Modulated by

TPM1 CH0

UART

modulation

SOPT5_UART1

TXSRC

—

UART1 UART1_TX to Modulated by

TPM2 CH0

UART

modulation

SOPT5_UART1

TXSRC

—

PIT TIF0 to DAC Advance DAC

FIFO

DAC HWTRG

Select

—

PIT TIF0 to DMA CH0 DMA HW

Trigger

DMA MUX

register option

—

PIT TIF1 to DMA CH1 DMA HW

Trigger

DMA MUX

register option

—

Chapter 3 Chip Configuration

KL25 Sub-Family Reference Manual, Rev. 3, September 2012

Freescale Semiconductor, Inc. 47

Loading...

Loading...